High-Performance Mixed-Signal Circuits

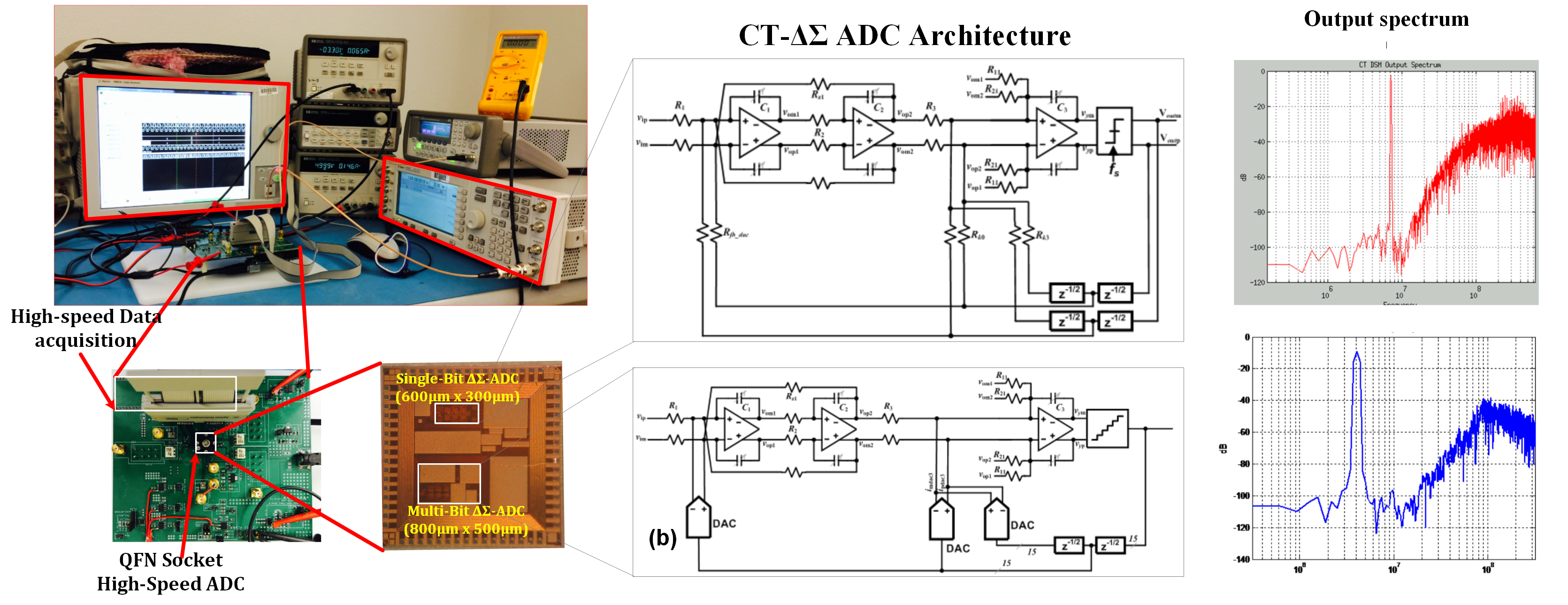

Rapid evolution of wireless broadband communication systems has necessitated development of power-efficient mixed-signal circuits with ever increasing signal bandwidth and flexibility of operation in multiple frequency bands. Challenges involve design of energy-efficient data converters in scaled nano-CMOS technologies where transistors offer high-speed although with poor gain and increased device variability. We have investigated novel analog-to-digital conversion architectures which will enable future wireless networks (IEEE 802.11ac+) and software-defined radios in nano-CMOS technologies. The architectures of interest include Continuous-time Delta-Sigma modulators with multi-step quantizers, Direct RF-to-digital conversion, Multi-band and Cascaded modulators. These architectures are expected to achieve wideband conversion (>25 MHz) with dynamic range >75 dB with figure of merit <100fJ/bit. Also of interest are phase locked loops with wide frequency range (900 MHz-5 GHz) and radio frequency front-ends for delta-sigma converters.