# ECE615 Mixed-Signal IC Design

#### Discrete-Time $\Delta\Sigma$ Modulator Implementation

Vishal Saxena, Boise State University (vishalsaxena@boisestate.edu)

Analog Mixed Signal IC Laboratory Boise State University

BOISE SIALE

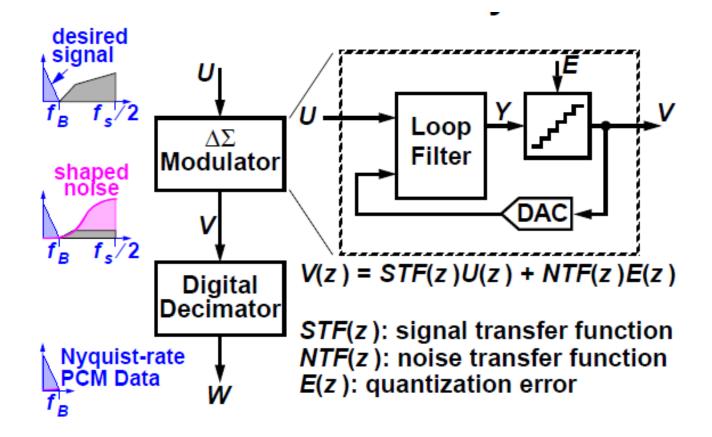

#### Review: A $\Delta\Sigma$ ADC System

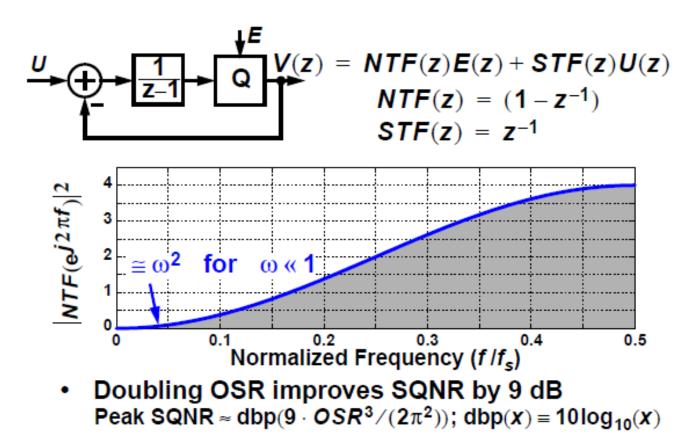

#### **Review: MOD1**

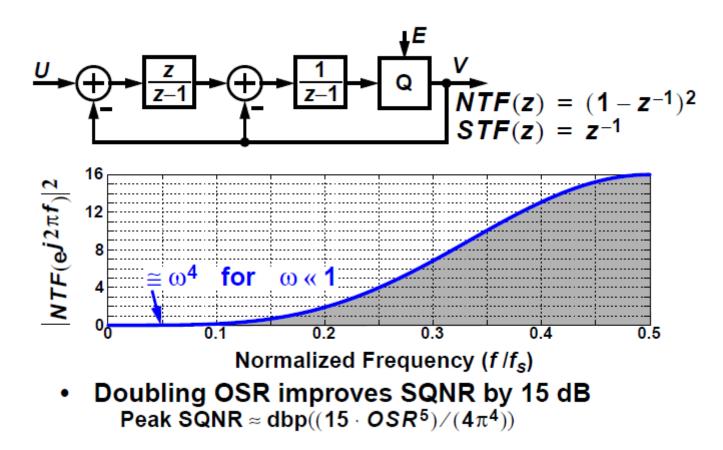

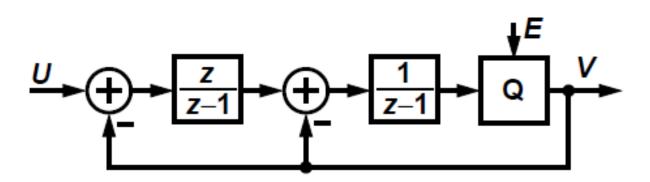

#### Review: MOD2

#### Review: Simulated MOD2 PSD

#### Input at 50% of FullScale 0 SQNR = 86 dB -20@ OSR = 128 -40 dBFS/NBW - Simulated spectrum -60 (smoothed) PSD Theoretical -80 -10040 dB/decade -120NBW = 5.7×10 -140 10-2 10<sup>-1</sup> $10^{-3}$ Normalized Frequency (f /fs)

#### Example Design 1

• Clock at fs = 1 MHz. Assume BW = 1 kHz.

$OSR = fs/(2 \cdot BW) = 500 \approx 29$

- MOD1: SQNR  $\approx$  9 dB/octave 9 octaves = 81 dB

- MOD2: SQNR  $\approx$  15 dB/octave 9 octaves =135 dB Actually more like 120 dB.

- SQNR of MOD1 is not bad, but SQNR of MOD2 is awesome!

MOD2 is usually preferred over MOD1 because MOD2's quantization noise is more well-behaved.

### **Block Diagram**

- Summation blocks

- **Delaying and non-delaying discrete-time**

- □ integrators

- Quantizer (1-bit)

- □ Feedback DACs (1-bit)

- Decimation filter (not shown)

- Digital and therefore "easy"

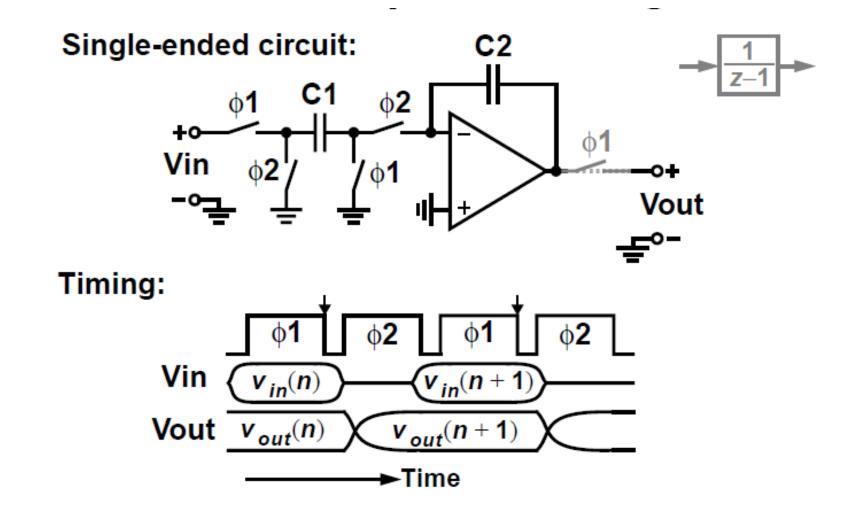

#### Switched-Capacitor Integrator

#### Switched-Capacitor Integrator contd.

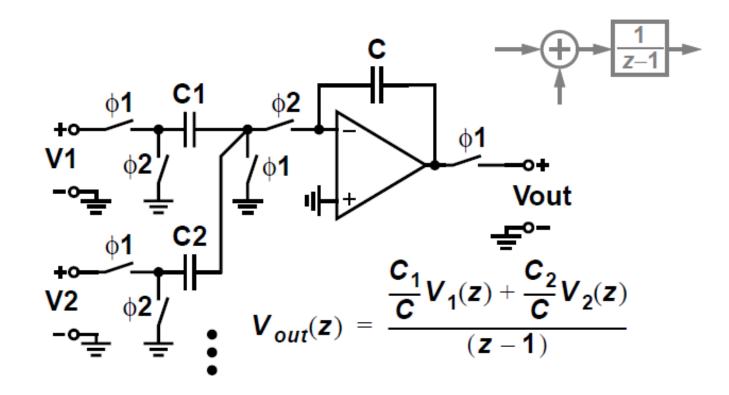

#### Summation and Integration

Adding an extra input branch accomplishes addition, with weighting

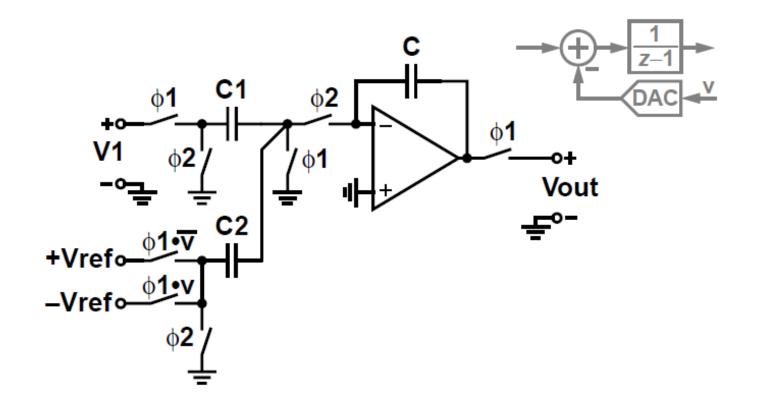

#### 1-bit DAC + Summation + Integration

Aug 27, 2013

© Vishal Saxena

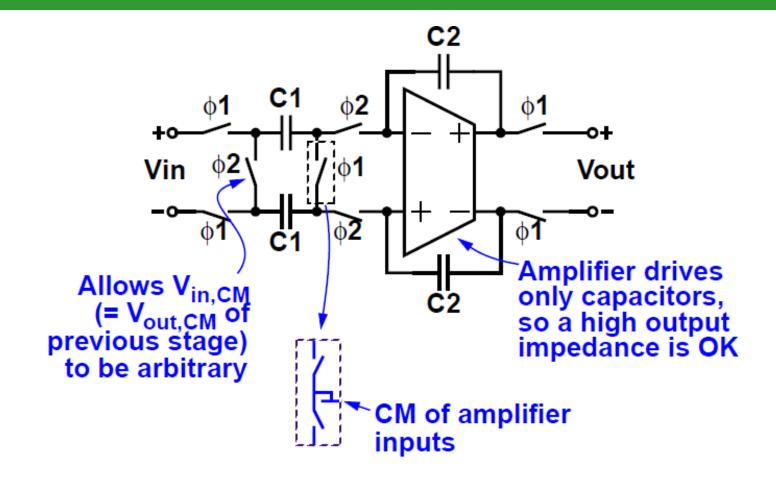

#### **Fully-Differential Integrator**

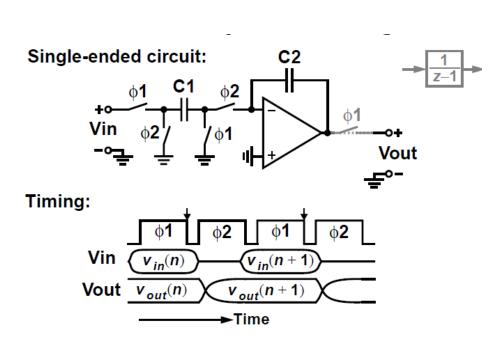

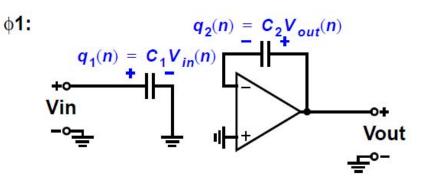

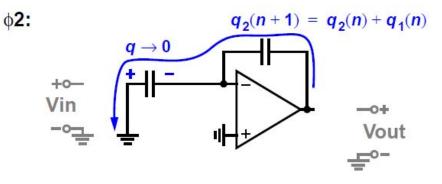

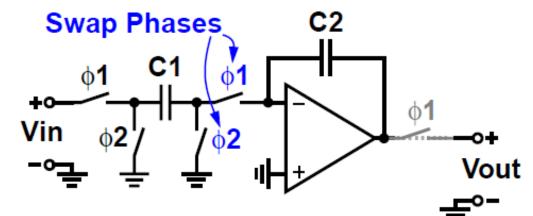

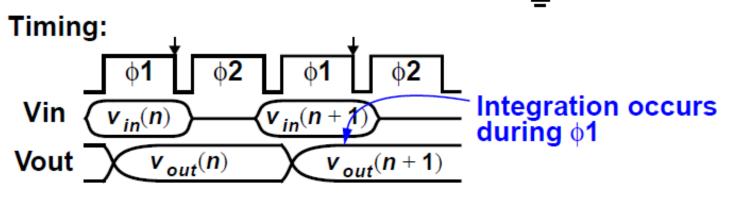

#### Non-Delaying Integrator

#### Single-ended circuit:

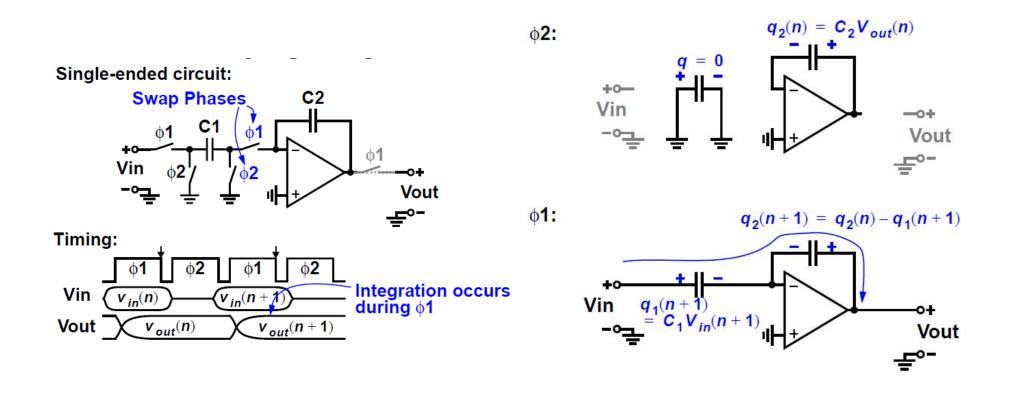

#### Non-Delaying Integrator contd.

#### Non-Delaying Integrator contd.

$$q_{2}(n+1) = q_{2}(n) - q_{1}(n+1)$$

$$z Q_{2}(z) = Q_{2}(z) - z Q_{1}(z)$$

$$\frac{Q_{2}(z)}{Q_{1}(z)} = -\frac{z}{z-1}$$

$$\frac{V_{out}(z)}{V_{in}(z)} = -\left(\frac{C_{1}}{C_{2}}\right)\frac{z}{z-1}$$

• Delaying (and inverting) integrator

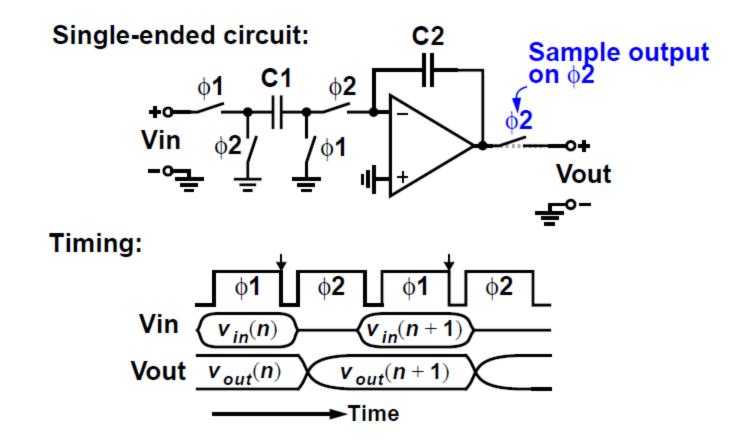

#### Half-Delay Integrator

#### Half-Delay Integrator

- Output is sampled on a different phase than the input

- **Some use the notation to denote the shift in sampling time**

$$H(z) = \frac{z^{-1/2}}{z-1}$$

- □ An alternative method is to declare that the border between time *n* and *n*+1 occurs at the end of a specific phase, say  $\varphi_2$

- A circuit which samples on  $\varphi_1$  and updates on  $\varphi_2$  is non-delaying, i.e. H(z) = z/(z-1)

whereas a circuit which samples on  $\varphi_2$  and updates on  $\varphi_1$  is delaying, i.e. H(z) = 1/(z-1)

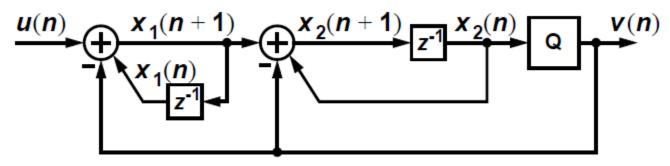

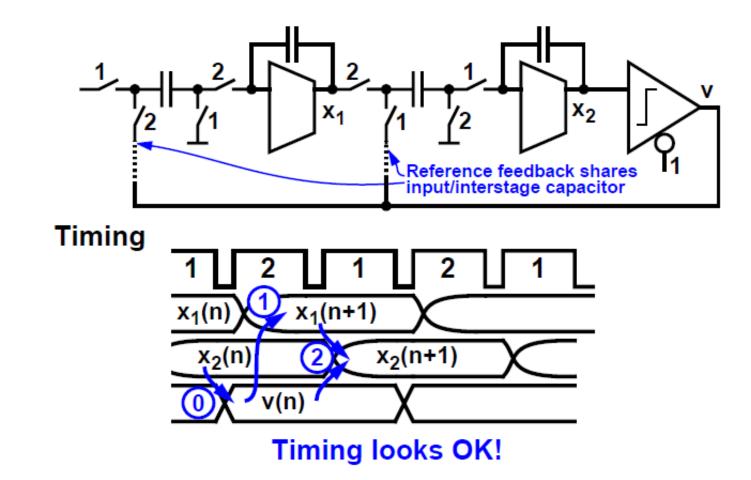

#### Timing in a $\Delta\Sigma$ Modulator

- The safest way to deal with timing is to construct a timing diagram and verify that the circuit implements the desired difference equations

- **E.g. MOD2:**

**Difference Equations:**

$$\begin{aligned} &v(n) = Q(x_2(n)) \\ &x_2(n+1) = x_2(n) - v(n) + x_1(n+1) \\ &x_1(n+1) = x_1(n) - v(n) + u(n) \end{aligned}$$

#### **Switched-Capacitor Realization**

## Signal Swing

- So far, we have not paid any attention to how much swing the op amps can support, or to the magnitudes of u, V<sub>ref</sub>, x<sub>1</sub> and x<sub>2</sub>

- For simplicity, assume: the full-scale range of u is ±1 V, the op-amp swing is also ±1 V and V<sub>ref</sub> = 1 V

- We still need to know the ranges of x<sub>1</sub> and x<sub>2</sub> in order to accomplish dynamic-range scaling

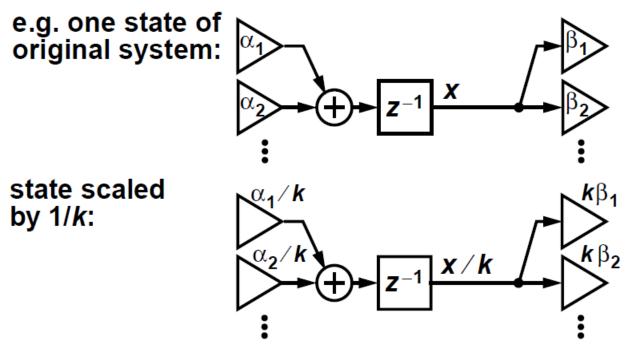

#### Dynamic Range Scaling

In a linear system with known state bounds, the states can be scaled to occupy any desired range

Aug 27, 2013

© Vishal Saxena