# SAR, Algorithmic and Integrating ADCs

Vishal Saxena, Boise State University (vishalsaxena@boisestate.edu)

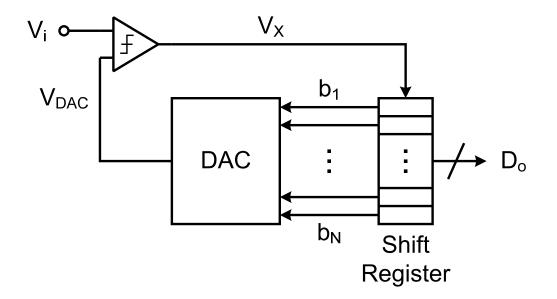

# Successive Approximation ADC

# Successive Approximation ADC

- Binary search algorithm  $\rightarrow N^*T_{clk}$  to complete N bits

- Conversion speed is limited by comparator, DAC, and digital logic (successive approximation register or SAR)

# **Binary Search Algorithm**

- DAC output gradually approaches the input voltage

- Comparator differential input gradually approaches zero

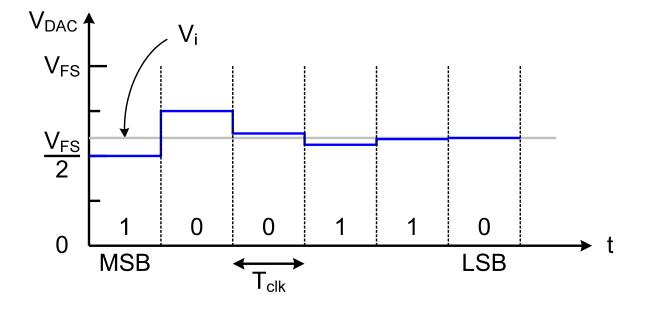

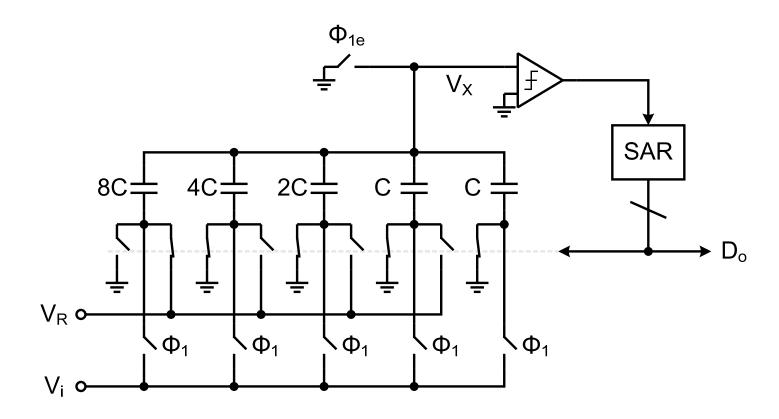

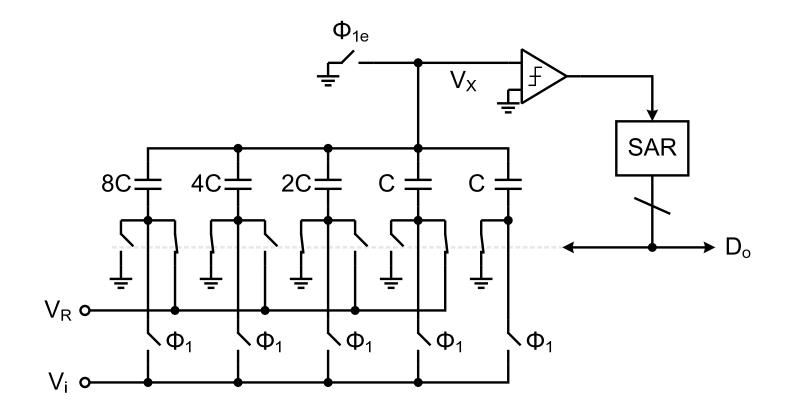

# Charge Redistribution SA ADC

- 4-bit binary-weighted capacitor array DAC (*aka* charge scaling DAC)

- Capacitor array samples input when  $\Phi_1$  is asserted (bottom-plate)

- Comparator acts as a zero crossing detector

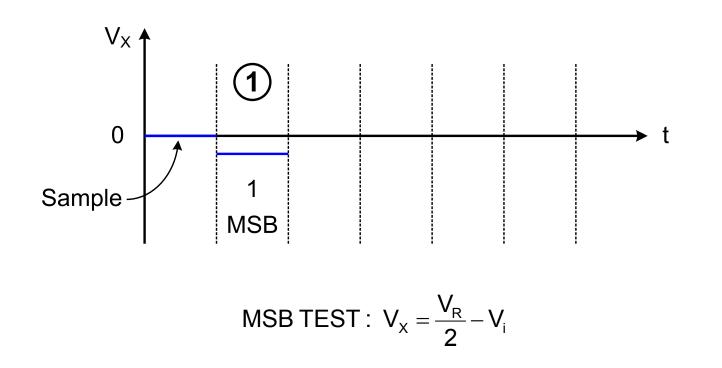

# Charge Redistribution (MSB)

• Start with C<sub>4</sub> connected to V<sub>R</sub> and others to 0 (i.e. SAR=1000)

$$V_{i} \cdot 16C = (V_{R} - V_{X})C_{4} - V_{X}(C_{3} + C_{2} + C_{1} + C_{0}) \implies V_{X} = \frac{V_{R} \cdot 8C - V_{i} \cdot 16C}{16C} = \frac{V_{R}}{2} - V_{i}$$

# Comparison (MSB)

- If  $V_X < 0$ , then  $V_i > V_R/2$ , and MSB = 1,  $C_4$  remains connected to  $V_R$

- If  $V_X > 0$ , then  $V_i < V_R/2$ , and MSB = 0,  $C_4$  is switched to ground

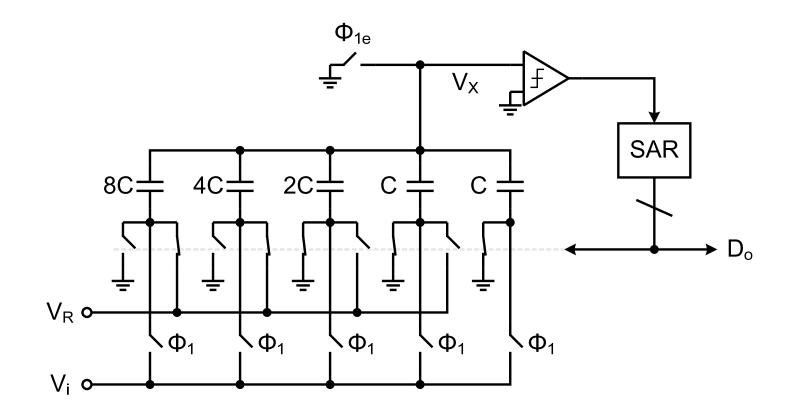

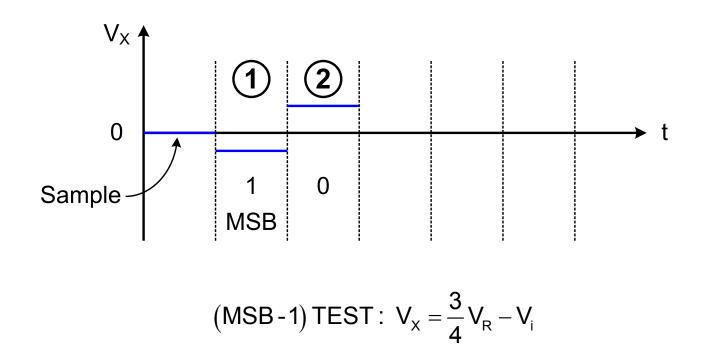

# Charge Redistribution (MSB-1)

• SAR=1100

$$V_{i} \cdot 16C = (V_{R} - V_{X}) \cdot 12C - V_{X} \cdot 4C \implies V_{X} = \frac{V_{R} \cdot 12C - V_{i} \cdot 16C}{16C} = \frac{3}{4}V_{R} - V_{i}$$

# Comparison (MSB-1)

- If  $V_X < 0$ , then  $V_i > 3V_R/4$ , and MSB-1 = 1,  $C_3$  remains connected to  $V_R$

- If  $V_X > 0$ , then  $V_i < 3V_R/4$ , and MSB-1 = 0,  $C_3$  is switched to ground

# Charge Redistribution (Other Bits)

• SAR=1010, and so on...

Test completes when all four bits are determined w/ four charge redistributions and comparisons

## After Four Clock Cycles...

- Usually, half T<sub>clk</sub> is allocated for charge redistribution and half for comparison + digital logic

- $V_X$  always converges to 0 ( $V_{os}$  if comparator has nonzero offset)

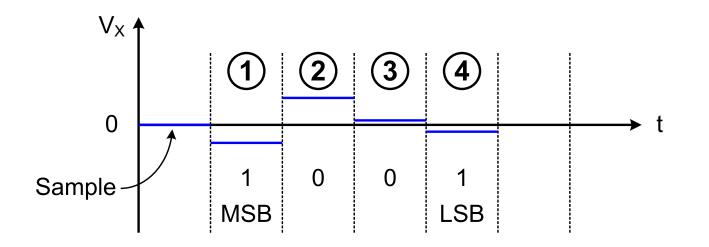

# **Summing-Node Parasitics**

- If  $V_{os} = 0$ ,  $C_P$  has no effect eventually; otherwise,  $C_P$  attenuates  $V_X$

- Auto-zeroing can be applied to the comparator to reduce offset

# SAR ADC Summary

- High accuracy achievable (12+ Bits)

- Low power and linear as no Opamp is required

- Relies on highly accurate comparator

- Moderate speed (10 MHz)

- Regaining interest in scaled CMOS processes

# **SAR ADC Limitations**

•Conversion rate typically limited by finite bandwidth of RC network during sampling and bit-tests

•For high resolution, the binary weighted capacitor array can become quite large

•E.g. 16-bit resolution, C<sub>total</sub>~100pF for reasonable kT/C noise contribution •If matching is an issue, an even larger value may be needed

•E.g. if matching dictates  $C_{min}$ =10fF, then 2<sup>16</sup> $C_{min}$ =655pF

Commonly used techniques

•Implement "two-stage" or "multi-stage" capacitor network to reduce array size [Yee, JSSC 8/79]

•Split DAC or C-2C network

•Calibrate capacitor array to obtain precision beyond raw technology matching [Lee, JSSC 12/84]

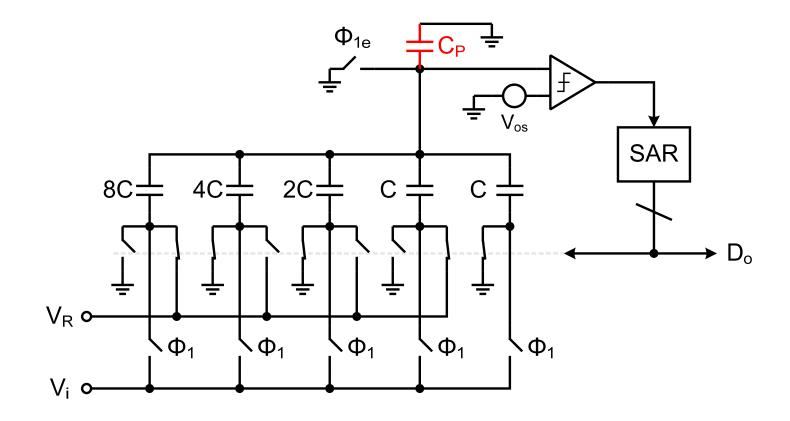

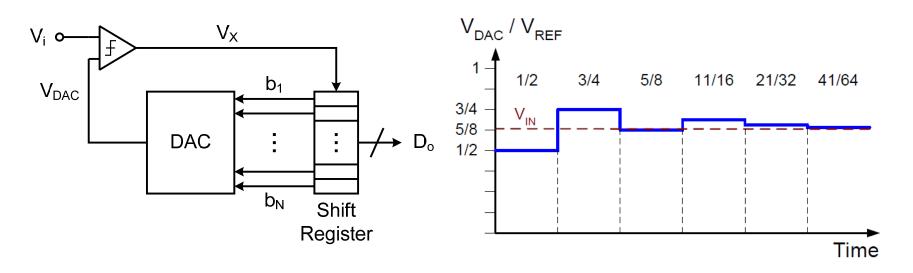

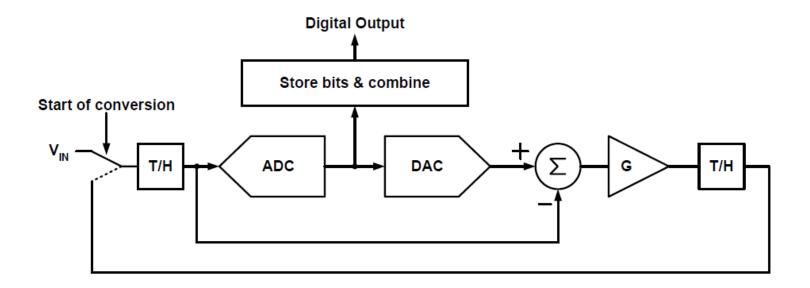

# Algorithmic (Cyclic) ADC

# Algorithmic (Cyclic) ADC

•Essentially same as pipeline

- •But a single MDAC stage is used in a cyclic fashion for all operations

- Need many clock cycles per conversion

# Algorithmic (Cyclic) ADC

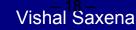

- Input is sampled first, then circulates in the loop for N clock cycles

- Conversion takes N cycles with one bit resolved in each T<sub>clk</sub>

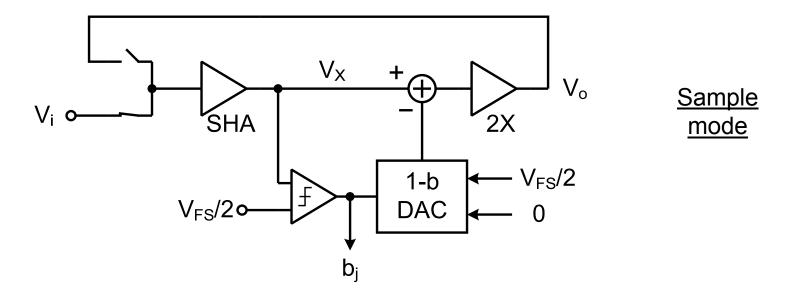

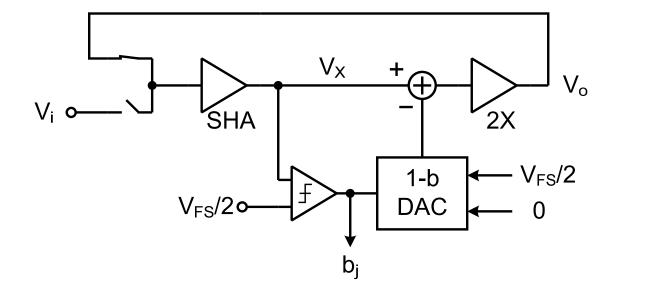

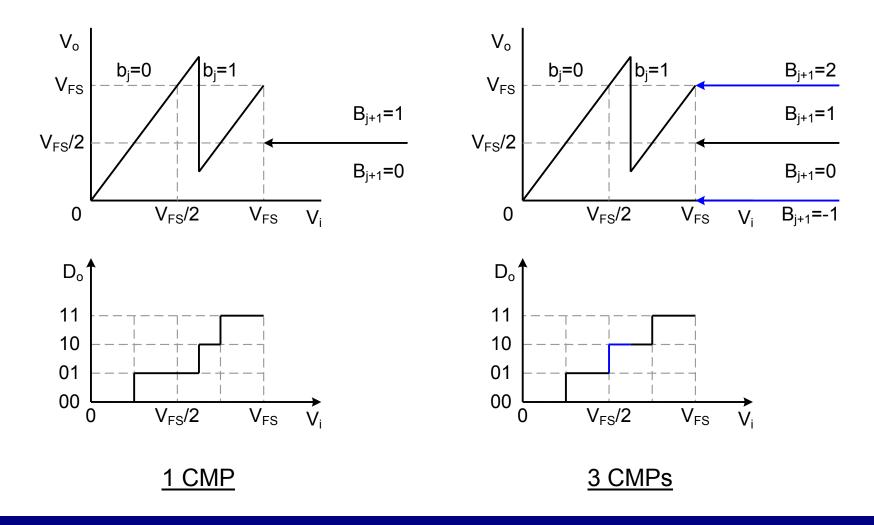

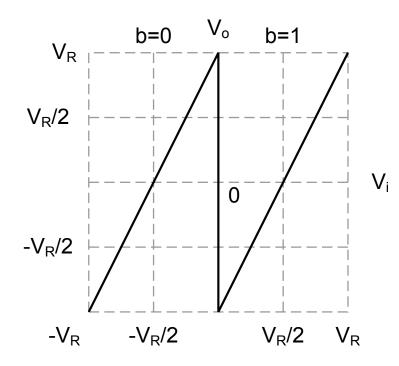

## Modified Binary Search

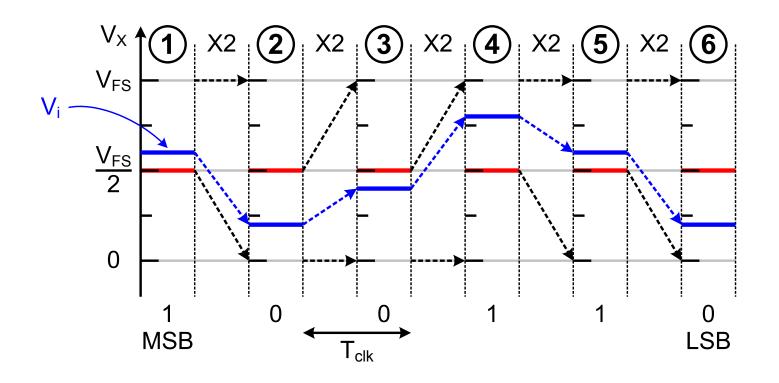

- If  $V_X < V_{FS}/2$ , then  $b_j = 0$ , and  $V_o = 2^*V_X$

- If  $V_X > V_{FS}/2$ , then  $b_j = 1$ , and  $V_o = 2^*(V_X V_{FS}/2)$

- V<sub>o</sub> is called conversion "residue"

- RA = residue amplifier

# **Modified Binary Search**

- Constant threshold ( $V_{FS}/2$ ) is used for each comparison

- Residue experiences 2X gain each time it circulates the loop

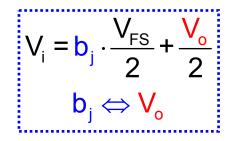

#### **Loop Transfer Function**

• Comparison  $\rightarrow$  if  $V_X < V_{FS}/2$ , then  $b_i = 0$ ; otherwise,  $b_i = 1$

• Residue generation  $\rightarrow V_o = 2^*(V_X - b_i^*V_{FS}/2)$

# Algorithmic ADC

- Hardware-efficient, but relatively low conversion speed (bit-per-step)

- Modified binary search algorithm

- Loop-gain (2X) requires the use of a residue amplifier, but greatly simplifies the DAC → 1-bit, inherently linear (why?)

- Residue gets amplified in each circulation; the gain accumulated makes the later conversion steps insensitive to circuit noise and distortion

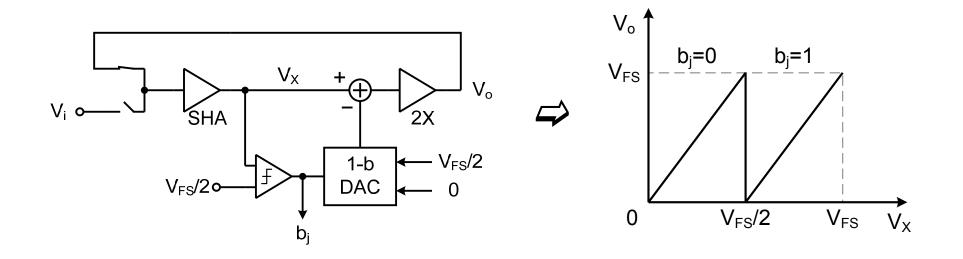

- Conversion errors (residue error due to comparator offset and/or loop-gain non-idealities) made in earlier conversion cycles also get amplified again and again – overall accuracy is usually limited by the MSB conversion step

- Redundancy is often employed to tolerate comparator/loop offsets

- Trimming/calibration/ratio-independent techniques are often used to treat loop-gain error, nonlinearity, etc.

#### **Offset Errors**

Vishal Saxena

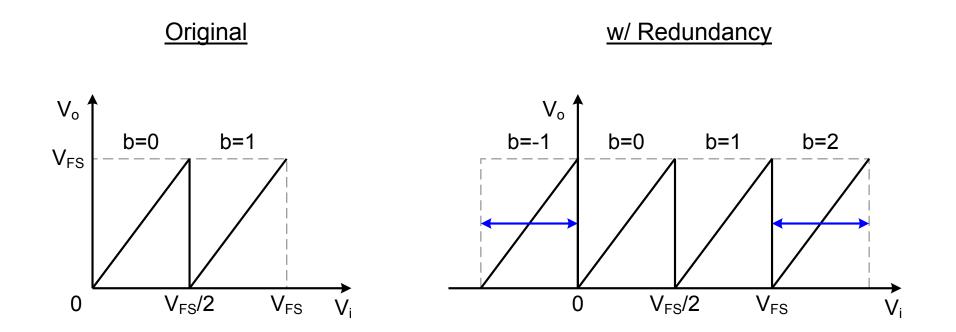

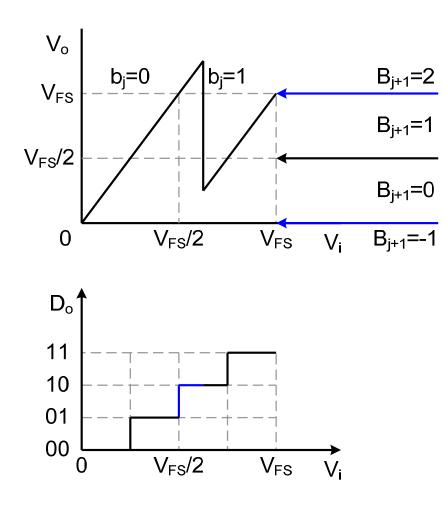

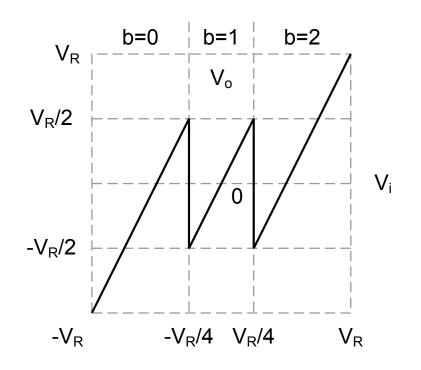

# Redundancy (DEC, RSD)

• RSD= Redundant Signed Digit

# Loop Transfer Function

- Subtraction/addition both required to compute final sum

- 4-level (2-bit) DAC required instead of 2-level (1-bit) DAC

#### Comparator Offset

- Max tolerance of comparator offset is  $\pm V_{FS}/4 \rightarrow simple$  comparators

- Similar tolerance also applies to RA offset

- Key to understand digital redundancy:

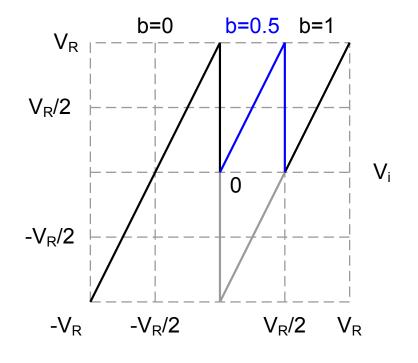

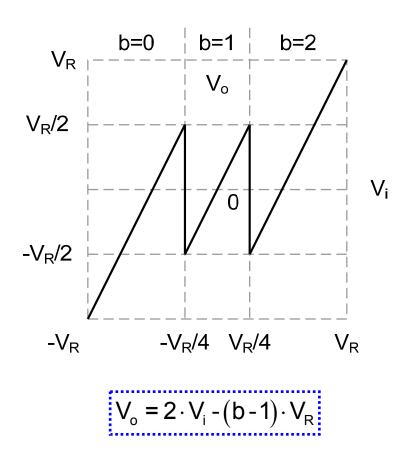

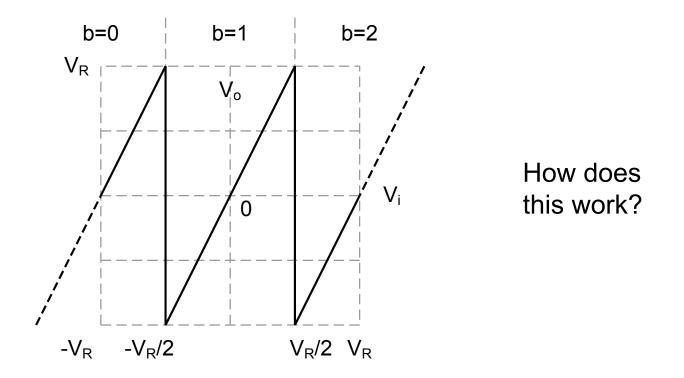

# Modified 1-Bit Architecture

1-b/s RA transfer curve w/ no redundancy One extra CMP added at  $V_R/2$

#### From 1-Bit to 1.5-Bit Architecture

A systematic offset  $-V_R/4$  introduced to both CMPs

A 2X scaling is performed on all output bits

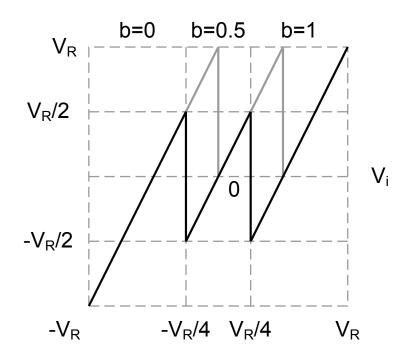

#### The 1.5-Bit Architecture

- 3 decision levels  $\rightarrow ENOB = \log_2 3 = 1.58$

- Max tolerance of comparator offset is ±V<sub>R</sub>/4

- An implementation of the Sweeny-Robertson-Tocher (SRT) division principle

- The conversion accuracy solely relies on the loop-gain error, i.e., the gain error and nonlinearity

- A 3-level DAC is required

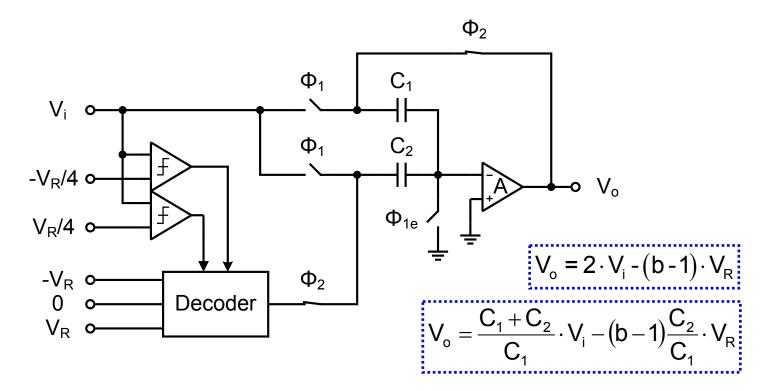

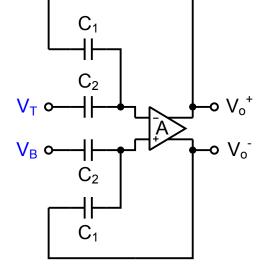

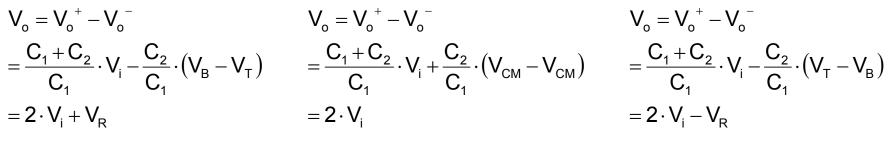

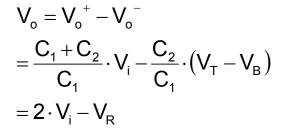

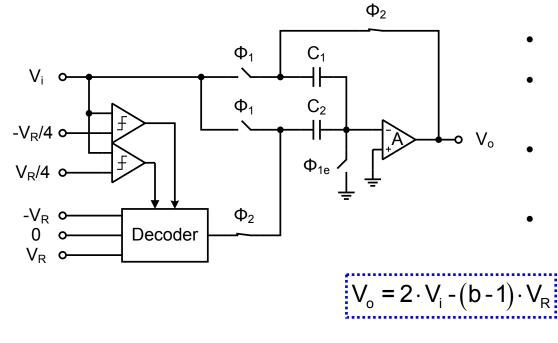

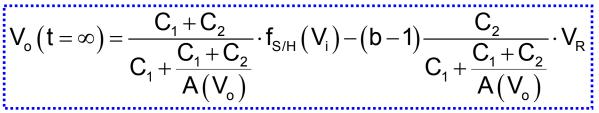

# The Multiplier DAC (MDAC)

- 2X gain + 3-level DAC + subtraction all integrated

- A 3-level DAC is perfectly linear in fully-differential form

- Can be generalized to n.5-b/stage architectures

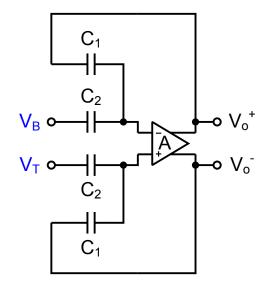

#### A Linear 3-Level DAC

$V_{o} = V_{o}^{+} - V_{o}^{-}$  $= 2 \cdot V_i + V_R$

Vishal Saxena

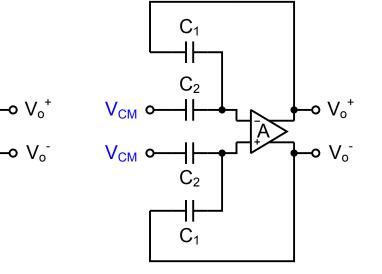

#### Alternative 1.5-Bit Architecture

<u>Ref</u>: E. G. Soenen and R. L. Geiger, "An architecture and an algorithm for fully digital correction of monolithic pipelined ADC's," *IEEE Trans. on Circuits and Systems II,* vol. 42, issue 3, pp. 143-153, 1995.

#### Error Mechanisms of RA

- Capacitor mismatch

- Op-amp finite-gain error and nonlinearity

- Charge injection and clock feedthrough (S/H)

- Finite circuit bandwidth

# RA Gain Error and Nonlinearity

Raw accuracy is usually limited to 10-12 bits w/o error correction

# Static Gain-Error Correction

#### Analog-domain method:

$$V_{o} = \frac{C_{1} + C_{2}}{C_{1} + \frac{C_{1} + C_{2}}{A}} \cdot V_{i} - b \cdot \frac{C_{2}}{C_{1} + \frac{C_{1} + C_{2}}{A}} \cdot V_{R} = \frac{ka_{1} \cdot V_{i} - b \cdot (ka_{2} \cdot V_{R})}{ka_{1} \cdot V_{i} - b \cdot (ka_{2} \cdot V_{R})}$$

Digital-domain method:

$$\left(\frac{V_{i}}{V_{R}}\right) = \frac{C_{1} + \frac{C_{1} + C_{2}}{A}}{C_{1} + C_{2}} \cdot \left(\frac{V_{o}}{V_{R}}\right) + \frac{C_{2}}{C_{1} + C_{2}} \cdot b \implies D_{i} = \mathbf{kd}_{1} \cdot D_{o} + \mathbf{kd}_{2} \cdot b$$

Do we need to correct for kd<sub>2</sub> error?

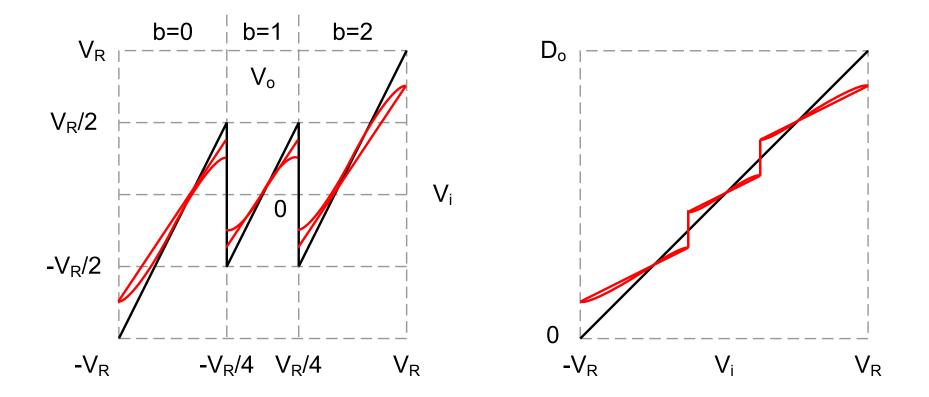

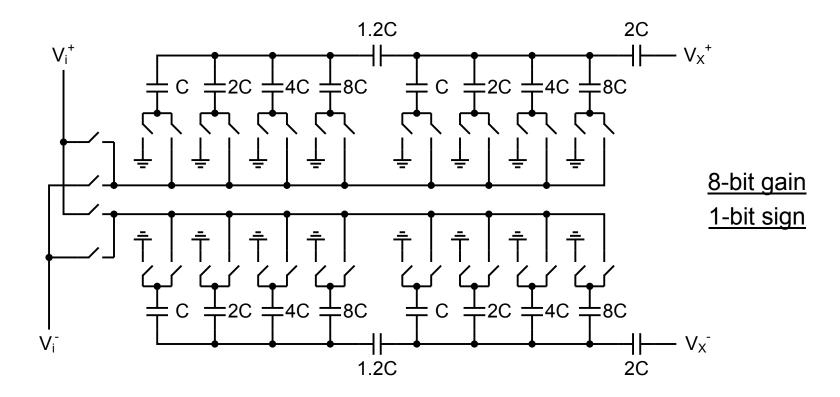

# **RA** Gain Trimming

- Precise gain-of-two is achieved by adjustment of the trim array

- Finite-gain error of op-amp is also compensated (**not nonlinearity**)

# Split-Array Trimming DAC

- Successive approximation utilized to find the correct gain setting

- Coupling cap is slightly increased to ensure segmental overlap

### **Digital Radix Correction**

$$\left(\frac{V_{i}}{V_{R}}\right) = \frac{C_{1} + \frac{C_{1} + C_{2}}{A}}{C_{1} + C_{2}} \cdot \left(\frac{V_{o}}{V_{R}}\right) + \frac{C_{2}}{C_{1} + C_{2}} \cdot b \implies D_{i} = kd_{1} \cdot D_{o} + kd_{2} \cdot b$$

#### Unroll this:

$$D_{j} = kd_{2} \cdot b_{j} + kd_{1} \cdot D_{j+1}$$

=  $kd_{2} \cdot b_{j} + kd_{1} \cdot (kd_{2} \cdot b_{j+1} + kd_{1} \cdot D_{j+2})$

=  $(kd_{2} \cdot b_{j}) + kd_{1} \cdot (kd_{2} \cdot b_{j+1}) + kd_{1}^{2} \cdot D_{j+2}$

=  $(kd_{2} \cdot b_{j}) + kd_{1} \cdot (kd_{2} \cdot b_{j+1}) + kd_{1}^{2} \cdot (kd_{2} \cdot b_{j+2}) + kd_{1}^{3} \cdot D_{j+3}$

=  $(kd_{2} \cdot b_{j}) + kd_{1} \cdot (kd_{2} \cdot b_{j+1}) + kd_{1}^{2} \cdot (kd_{2} \cdot b_{j+2}) + kd_{1}^{3} \cdot (kd_{2} \cdot b_{j+3}) + \dots$

# Integrating ADC

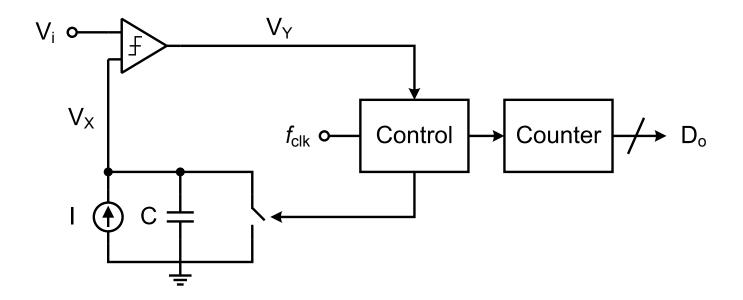

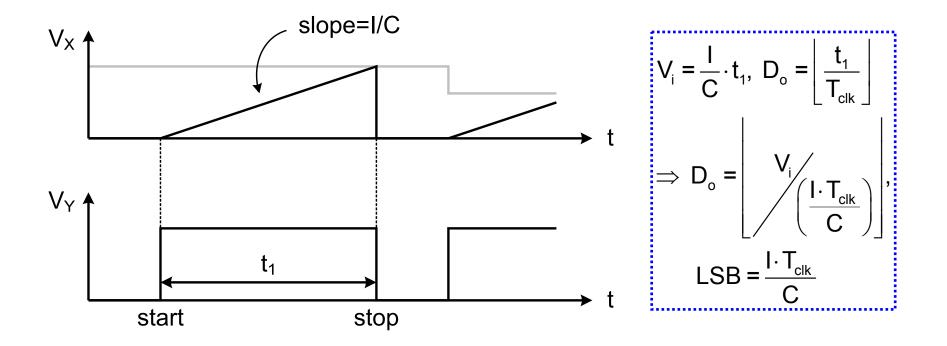

# Single-Slope Integration ADC

- Sampled-and-held input (V<sub>i</sub>)

- Counter keeps counting until comparator output toggles

- Simple, inherently monotonic, but very slow (2<sup>N</sup>\*T<sub>clk</sub>/sample)

# Single-Slope Integration ADC

- INL depends on the linearity of the ramp signal

- Precision capacitor (C), current source (I), and clock (T<sub>clk</sub>) required

- Comparator must handle wide input range of [0, V<sub>FS</sub>]

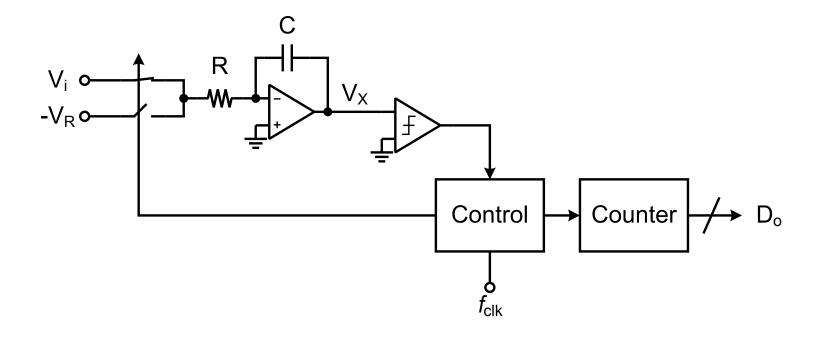

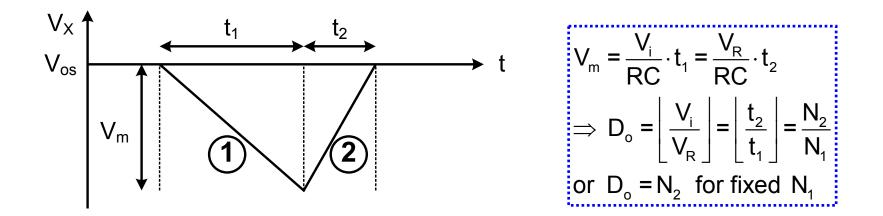

# **Dual-Slope Integration ADC**

- RC integrator replaces the I-C integrator

- Input and reference voltages undergo the same signal path

- Comparator only detects zero crossing

# **Dual-Slope Integration ADC**

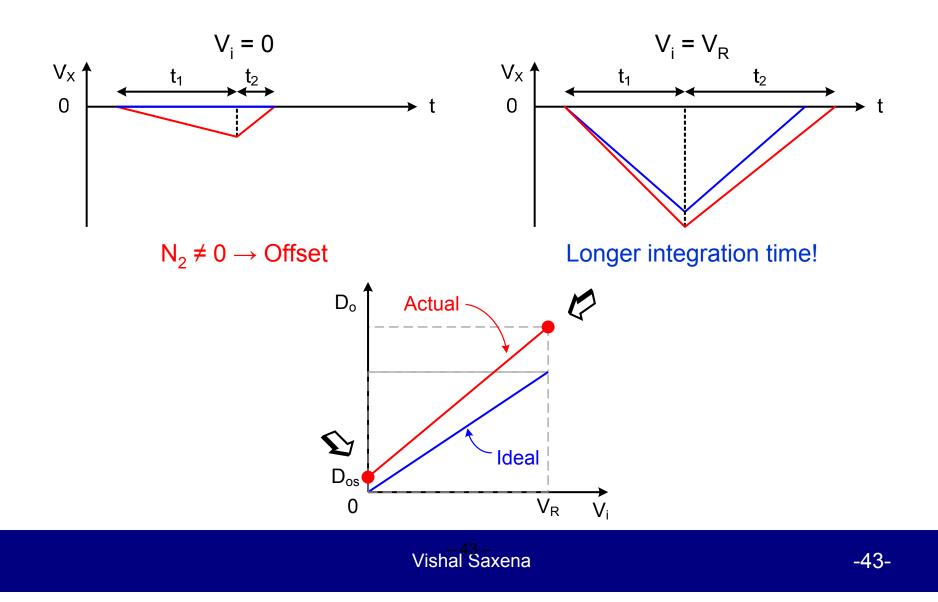

- Exact values of R, C, and T<sub>clk</sub> are not required

- Comparator offset doesn't matter (what about its delay?)

- Op-amp offset introduces gain error and offset (why?)

- Op-amp nonlinearity introduces INL error

#### **Op-Amp Offset**

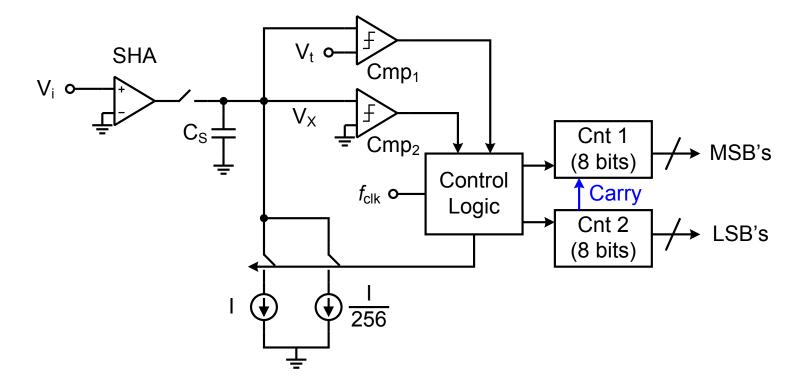

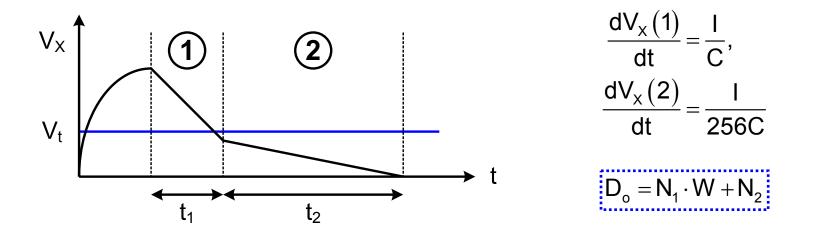

# Subranging Dual-Slope ADC

- MSB discharging stops at the immediate next integer count past V<sub>t</sub>

- Much faster conversion speed compared to dual-slope

- Two current sources (matched) and two comparators required

#### Subranging Dual-Slope ADC

- Precise V<sub>t</sub> is not required if carry is propagated

- Matching between the current sources is critical  $\rightarrow$  if I<sub>1</sub> = I, I<sub>2</sub> = (1+ $\delta$ )·I/256, then  $|\delta| \le 0.5/256$

- It'd be nice if CMP 1 can be eliminated  $\rightarrow$  ZX detector!

# Subranging Dual-Slope ADC

- CMP 1 response time is not critical

- Delay from CNT 1 to MSB current shut-off is not critical

→ constant delay results in an offset (why?)

- CMP 2 response time is critical, but relaxed due to subranging

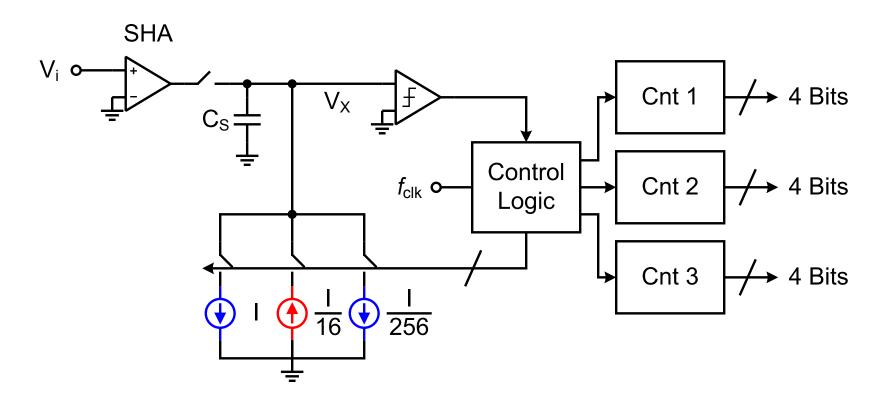

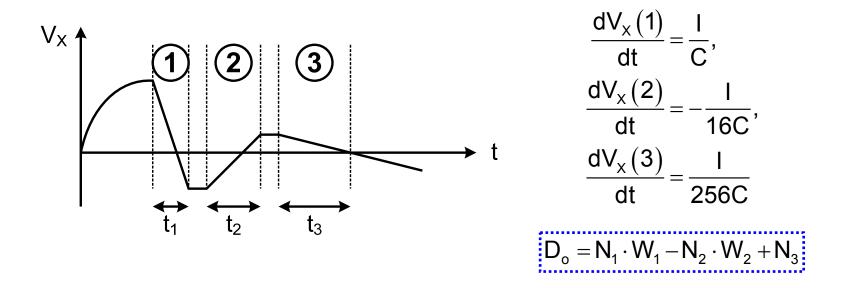

### Subranging Multi-Slope ADC

<u>Ref</u>: J.-G. Chern and A. A. Abidi, "An 11 bit, 50 kSample/s CMOS A/D converter cell using a multislope integration technique," in *Proceedings of IEEE Custom Integrated Circuits Conference*, 1989, pp. 6.2/1-6.2/4.

# Subranging Multi-Slope ADC

- Single comparator detects zero-crossing

- Comparator response time greatly relaxed

- Matching between the current sources still critical

# Subranging Multi-Slope ADC

- Comparator response time is not critical except the last one

- Delays from CNTs to current sources shut-off are not critical

→ constant delays only result in offsets

- Last comparator response time is critical, but relaxed due to multistep subranging

# References

- 1. Rudy van de Plassche, "CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters," 2<sup>nd</sup> Ed., Springer, 2005..

- 2. Y. Chiu, *Data Converters Lecture Slides*, UT Dallas 2012.

- B. Boser, Analog-Digital Interface Circuits Lecture Slides, UC Berkeley 2011.