## Homework 5

## ECE 5/411 - CMOS Analog IC Design

## Note:

1. Use Cadence schematic capture, layout and Spectre simulation tools, available on the AMS servers for the homework problems.

2. Use the  $1 \mu m$  CMOS parameters from Table 1 posted on the site, along with the corresponding Spectre models.

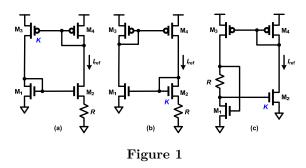

- **Problem 1:** The beta-multiplier references (BMR) are used for constant- $g_m$  biasing, where the goal is to stabilize the transconductance of a transistor. For example, in Fig. 1 (a), the  $g_m$  of M1 will be 'copied' to a current mirror device (not shown here).

- a) Derive expressions for  $I_{ref}$ ,  $V_{GS_1}$  and  $g_{m1}$  in Fig. 1 (a). Note that M3 is K times wider than M4 and M1 and M2 are the same size. Draw the schematic for a start-up circuit for this BMR.

- b) Will the circuit shown in Fig. 1 (b) work as a constant- $g_m$  reference? Explain.

- c) Fig. 1 (c) shows a fix for the body effect problem in the bottom NMOS in the BMR. Derive an equation for  $I_{ref}$  in this circuit. Run a temperature sweep on  $I_{ref}$  and compare it with the results from the BMR seen in class. Explain your observations.

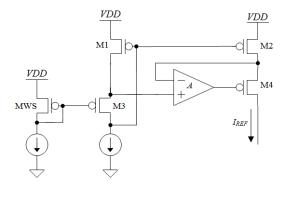

- **Problem 2:** Consider the PMOS-version of the regulated drain current mirror shown in Fig 2.

- a) Find expressions (in terms of  $V_{THP}$ ,  $V_{SD,sat}$ and  $V_{DD}$ ) for all the DC levels in the circuit.

- b) Estimate the small-signal output resistance,  $R_o$ , of the current mirror.

- c) What the allowed swing across the current mirror, to ensure all transistors are in saturation?

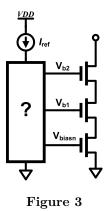

- **Problem 3:** The concept of cascoding can be further extended to realize a *triple-cascode* current mirror as shown below.

- a) Assuming all devices to be identical, find an expression for the output resistance of this triple-cascode current mirror? What are the trade-offs involved if double-cascoding is used in designs?

- b) Given an ideal reference  $(I_{ref})$  and using long-channel equations, design a wide-swing triple-cascode current mirror such that the minimum allowed output voltage is  $3V_{DS,sat}$ . Neatly show the schematics and the steps for

calculating the sizes of the long-length devices used in the design.

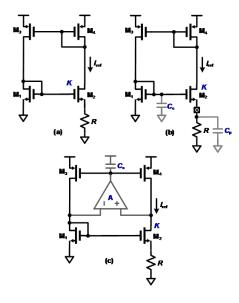

- **Problem 4:** This problem deals with the practical considerations for constant- $g_m$  bias (aka BMR) circuit design. Using the 180 nm CMOS process and the characterization data from HW3:

- a) Design and simulate a constant- $g_m$  bias circuit shown in Figure 4 (a), along with a start-up circuit. Plot the currents in the BMR when  $V_{DD}$  is swept. Comment on the supply sensitivity of the circuit.

- b) In practice, on-chip resistance varies by  $\pm 20\%$ and thus an external precision resistance may be used for setting the bias current as shown in Figure 4 (b). However, the bondpad introduces a parasitic capacitance (say  $C_p = 200 \ fF$ . This necessitates a compensation capacitance  $C_c$  to stabilitize the circuit. Modify your circuit from part (a) by including the bond-pad parasitic cap and stabilize the circuit.

- c) Repeat part (a), by using an ideal amplifier model to regulate the drain voltages of the bottom NMOS devices as shown in Figure 4 (c). Note that, later on when using transistor-level amplifier, the loop will need to be compensated.

Figure 4