## Short-Channel Analog Design Additional Slides

#### Vishal Saxena ECE, Boise State University

Feb 1, 2011

Vishal Saxena Short-Channel Design

- Circuit designers care about:

- Gain $\rightarrow g_m r_o$

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Noise

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Noise

- Linearity

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Noise

- Linearity

- Circuit matching

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Noise

- Linearity

- Circuit matching

- Layout designers:

- Gain $\rightarrow g_m r_o$

- Bandwidth $\rightarrow g_m, f_T, C_{gs}, C_{gs}$

- Power $\rightarrow I_D$

- Voltage Swing  $\rightarrow V_{DS,sat}$

- Noise

- Linearity

- Circuit matching

- Layout designers:

- mostly care about W/L, layout matching and circuit isolation (substrate noise)

#### Short Channel Characteristics

•

$$i_D = v_{sat} C'_{ox} (v_{GS} - V_{THN} - V_{DS,sat})$$

• Square law equations no longer valid (but intuition is!)

•

$$i_D = v_{sat} C_{ox}^{'} (v_{GS} - V_{THN} - V_{DS,sat})$$

• velocity saturation and overshoot effects

•

$$i_D = v_{sat} C_{ox}^{'} (v_{GS} - V_{THN} - V_{DS,sat})$$

- velocity saturation and overshoot effects

- Examples use the 50nm CMOS process from the textbook.

•

$$i_D = v_{sat} C_{ox}^{'} (v_{GS} - V_{THN} - V_{DS,sat})$$

- velocity saturation and overshoot effects

- Examples use the 50nm CMOS process from the textbook.

•

$$V_{DD} = 1V$$

.  $L_{min} = 50n$

•

$$i_D = v_{sat} C_{ox}^{'} (v_{GS} - V_{THN} - V_{DS,sat})$$

- velocity saturation and overshoot effects

- Examples use the 50nm CMOS process from the textbook.

•

$$V_{DD} = 1V$$

.  $L_{min} = 50n$

•

$$V_{THN} = V_{THP} = 280 \ mV$$

#### Short Channel Device Characteristics contd.

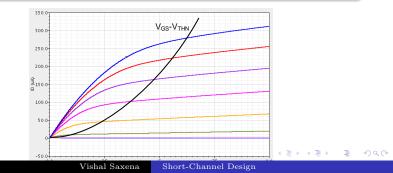

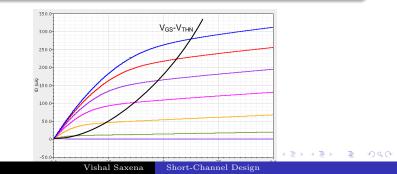

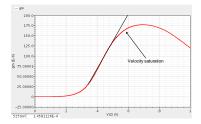

• The devices appear to go into saturation earlier than predicted by  $V_{DS,sat} = V_{GS} - V_{THN}$

#### Short Channel Device Characteristics contd.

- The devices appear to go into saturation earlier than predicted by  $V_{DS,sat} = V_{GS} V_{THN}$

- The actual charge distribution is a function of  $V_{DS}$  and  $Q'_{I}(y)$  becomes zero earlier (i.e. at a lower  $V_{DS,sat}$ ).

#### Short Channel Device Characteristics contd.

- The devices appear to go into saturation earlier than predicted by  $V_{DS,sat} = V_{GS} V_{THN}$

- The actual charge distribution is a function of  $V_{DS}$  and  $Q'_{I}(y)$  becomes zero earlier (i.e. at a lower  $V_{DS,sat}$ ).

- Is this good?

#### Short Channel Device Characteristics contd.

- The devices appear to go into saturation earlier than predicted by  $V_{DS,sat} = V_{GS} V_{THN}$

- The actual charge distribution is a function of  $V_{DS}$  and  $Q'_{I}(y)$  becomes zero earlier (i.e. at a lower  $V_{DS,sat}$ ).

- Is this good?

- Not really, need to look at the region where  $r_o$  is large and that occurs when the device is well into saturation :(

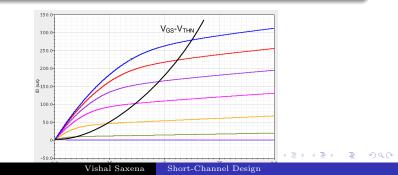

• For short channel devices, the relation  $V_{DS,sat} = V_{GS} - V_{THN}$  is meaningless

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

#### Short Channel contd.

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

#### Short Channel contd.

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

•

$$V_{ov} = 70 mV \rightarrow V_{GS} = 350 mV$$

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

•

$$V_{ov} = 70 mV \rightarrow V_{GS} = 350 mV$$

•

$$f_T \alpha \frac{V_{ov}}{L}$$

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

• We can use  $V_{ov} = 0.05 V_{DD}$  as a starting point for high-speed design (build your own intuition)

•

$$V_{ov} = 70 mV \rightarrow V_{GS} = 350 mV$$

•

$$f_T \alpha \frac{V_{ov}}{L}$$

• Use L = 2.5 times  $L_{min}$  for a good trade-off between speed and gain $\rightarrow L = 100n$

- For short channel devices, the relation  $V_{DS,sat} = V_{GS} V_{THN}$  is meaningless

- Now, we'll talk in terms of the gate overdrive voltage

•

$$V_{ov} = V_{GS} - V_{THN}

e V_{DS,sat}$$

•

$$V_{ov} = 70 mV \rightarrow V_{GS} = 350 mV$$

•

$$f_T \alpha \frac{V_{ov}}{L}$$

- Use L=2-5 times  $L_{min}$  for a good trade-off between speed and gain  ${\rightarrow}L=100n$

- Increasing  $V_{ov}$  results in higher speed, but at a cost of reduced output swing

## Low Frequency Incremental Model

• First order Taylor series expansion of  $i_D$

## Low Frequency Incremental Model

• First order Taylor series expansion of

$$i_D$$

•

$$i_d = \frac{\partial i_D}{\partial v_{GS}} v_{gs} + \frac{\partial i_D}{\partial v_{SB}} v_{sb} + \frac{\partial i_D}{\partial v_{DS}} v_{ds}$$

## Low Frequency Incremental Model

• First order Taylor series expansion of

$$i_D$$

•

$$i_d = \frac{\partial i_D}{\partial v_{GS}} v_{gS} + \frac{\partial i_D}{\partial v_{SB}} v_{sb} + \frac{\partial i_D}{\partial v_{DS}} v_{ds}$$

•

$$I_d = g_m v_{gs} + g_{mb} v_{sb} + g_{ds} v_{ds}$$

#### Low Frequency Incremental Model

• First order Taylor series expansion of  $i_D$

•

$$i_d = \frac{\partial i_D}{\partial v_{GS}} v_{gS} + \frac{\partial i_D}{\partial v_{SB}} v_{sb} + \frac{\partial i_D}{\partial v_{DS}} v_{dS}$$

•  $i_d = g_m v_{gS} + g_{mb} v_{sb} + g_{dS} v_{dS}$

• Just need to know the small signal parameters

#### Square Law Model

• In saturation region,  $g_m$  is given by

Vishal Saxena Short-Channel Design

# Square Law Model

• In saturation region,

$$g_m$$

is given by

•

$$g_m = \sqrt{2\beta I_D}$$

Vishal Saxena Short-Channel Design

- 4 同 ト 4 臣 ト 4 臣 ト

# Square Law Model

• In saturation region,

$$g_m$$

is given by

•

$$g_m = \sqrt{2\beta I_D}$$

•  $g_m = \beta V_{ov}$

<ロト <問 > < 臣 > < 臣 >

## Square Law Model

#### • In saturation region, $g_m$ is given by

•

$$g_m = \sqrt{2\beta I_D}$$

•  $g_m = \beta V_{ov}$

•  $g_m = \frac{2I_D}{V_{ov}}$

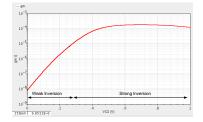

### Weak Inversion $g_m$

• In weak inversion (subthreshold) we have exponential I-V characteristics

### Weak Inversion $g_m$

• In weak inversion (subthreshold) we have exponential I-V characteristics

•

$$I_D \approx I_{D0} \frac{W}{L} e^{\frac{V_{GS} - V_{THN}}{nV_T}}$$

## Weak Inversion $g_m$

• In weak inversion (subthreshold) we have exponential I-V characteristics

•

$$I_D \approx I_{D0} \frac{W}{L} e^{\frac{V_{GS} - V_{THN}}{nV_T}}$$

•  $g_m = \frac{\partial i_D}{\partial v_{CS}} = \frac{I_D}{nV_T} \propto I_D$

### Transconductance

$$g_m = \beta \left( V_{GS} - V_{THN} \right)$$

$$g_{m_{sub-V_T}} = \frac{I_D}{nV_T}$$

イロト イヨト イヨト イヨト

æ

• Given  $V_{ov}$  and a specified  $g_m$ , pick  $I_D$  and W.

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- This leads to W=50 for NMOS and W=100 for PMOS.

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- This leads to W=50 for NMOS and W=100 for PMOS.

- More on this point later.

$\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

글▶ 글

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- This leads to W = 50 for NMOS and W = 100 for PMOS.

- $\bullet$  Given  $V_{ov}$  and a specified  $g_m,$  pick  $I_D$  and W.

- Here, for a  $g_m = 150 \frac{\mu A}{V}$  we pick  $I_D = 10 \mu A$  for sufficient current drive.

- This leads to W = 50 for NMOS and W = 100 for PMOS.

- More on this point later.

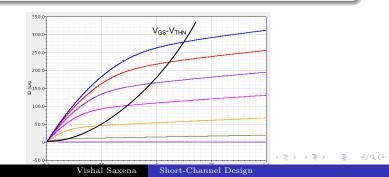

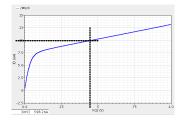

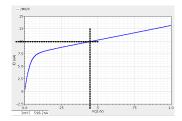

#### Output Resistance $r_o$

• To determine  $V_{DS,sat}$ , look at the point where the output resistance starts to increase (Here,  $V_{DS,sat} = 50mV$ )

### Output Resistance $r_o$

- To determine  $V_{DS,sat}$ , look at the point where the output resistance starts to increase (Here,  $V_{DS,sat} = 50mV$ )

- We get considerably higher output resistances at a larger  $V_{DS}($ important!)

### Output Resistance $r_o$

- To determine  $V_{DS,sat}$ , look at the point where the output resistance starts to increase (Here,  $V_{DS,sat} = 50mV$ )

- We get considerably higher output resistances at a larger  $V_{DS}(\text{important!})$

- Cannot just model by a simple equation  $r_o = \frac{1}{\lambda l_{0,st}}$

### Open-loop Gain $(g_m r_o)$

• The open loop gain is roughly  $g_m r_o = 150 \frac{\mu A}{V} \cdot 170 k \Omega \approx 25$

# Open-loop Gain $(g_m r_o)$

• The open loop gain is roughly  $g_m r_o = 150 \frac{\mu A}{V} \cdot 170 k\Omega \approx 25$ • considerably lower than the open-loop gain in a long channel process.

#### Transition Frequency

- $f_T$  for a 50/2 NMOS is around 4GHz.

- Can look at the  $f_T$  when  $V_{GS}$  is swept.

- The sizes an biasing selected in this example (from textbook) is a good starting point for a general design.

- If the sizes and biasing will eventually depend upon your design specifications.

- Also need to account for PVT shifts.

- Characterize the technology models well and generate a table for your selected design parameters.

## Design Table

| Short-channel MOSFET parameters for general analog design<br>VDD = 1 V and a scale factor of <b>50 nm</b> (scale = 50e-9) |                             |                             |                                                         |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|---------------------------------------------------------|

| Parameter                                                                                                                 | NMOS                        | PMOS                        | Comments                                                |

| Bias current, $I_D$                                                                                                       | 10 µA                       | 10 µA                       | Approximate, see Fig. 9.31                              |

| W/L                                                                                                                       | 50/2                        | 100/2                       | Selected based on $I_D$ and $V_{ov}$                    |

| Actual W/L                                                                                                                | 2.5µm/100nm                 | 5µm/100nm                   | L <sub>min</sub> is 50 nm                               |

| $V_{	extsf{DS,sat}} 	extsf{ and } V_{	extsf{SD,sat}} \ V_{	extsf{onn}} 	extsf{ and } V_{	extsf{onp}}$                     | 50 mV<br>70 mV              | 50 mV<br>70 mV              | However, see Fig. 9.32 and<br>the associated discussion |

| $V_{\rm GS}$ and $V_{\rm SG}$                                                                                             | $350 \mathrm{mV}$           | $350 \mathrm{mV}$           | No body effect                                          |

| V <sub>THN</sub> and V <sub>THP</sub>                                                                                     | 280 mV                      | 280 mV                      | Typical                                                 |

| $\partial V_{THN,P} / \partial T$                                                                                         | $-0.6 \text{ mV/C}^{\circ}$ | $-0.6 \text{ mV/C}^{\circ}$ | Change with temperature                                 |

| $v_{sam}$ and $v_{sam}$                                                                                                   | 110 x 10 <sup>3</sup> m/s   | 90 x 10 <sup>3</sup> m/s    | From the BSIM4 model                                    |

| t <sub>ax</sub>                                                                                                           | 14 Å                        | 14 Â                        | Tunnel gate current, 5 A/cm <sup>2</sup>                |

| $C'_{ox} = \epsilon_{ox}/t_{ox}$                                                                                          | $25 f F/\mu m^2$            | $25 f F/\mu m^2$            | $C_{ox} = C'_{ox}WL \cdot (scale)^2$                    |

| $C_{onn}$ and $C_{onp}$                                                                                                   | 6.25 <i>f</i> F             | 12.5 <i>f</i> F             | PMOS is two times wider                                 |

| $C_{gan}$ and $C_{zgp}$                                                                                                   | 4.17 <i>f</i> F             | 8.34 <i>f</i> F             | $C_{gz} = \frac{2}{3}C_{ox}$                            |

| $C_{\rm gab}$ and $C_{\rm dgp}$                                                                                           | 1.56 <i>f</i> F             | 3.7 <i>f</i> F              | $C_{gd} = CGDO \cdot W \cdot scale$                     |

| $g_{nm}$ and $g_{np}$                                                                                                     | 150 μA/V                    | 150 μA/V                    | At $I_D = 10 \ \mu A$                                   |

| $r_{on}$ and $r_{op}$                                                                                                     | 167 kΩ                      | 333 kΩ                      | Approximate at $I_D = 10 \ \mu A$                       |

| $g_{nm}r_{on}$ and $g_{np}r_{op}$                                                                                         | 25 V/V                      | 50 V/V                      | !!Open circuit gain!!                                   |

| $\lambda_n$ and $\lambda_p$                                                                                               | 0.6 V <sup>-1</sup>         | 0.3 V <sup>-1</sup>         | L = 2                                                   |

| $f_{In}$ and $f_{Ip}$                                                                                                     | 6000 MHz                    | 3000 MHz                    | Approximate at $L = 2$                                  |

Table 9.2 Typical parameters for analog design using the *short-channel* CMOS process discussed in this book. These parameters are valid only for the device sizes and currents listed.

・ロト ・ 日 ト ・ ヨ ト ・ ヨ ト

æ

### References I

R. J. Baker, CMOS Circuit Design, Layout and Simulation, revised 2nd Edition, Wiley-IEEE, 2008.

< • • • **6**

ъ