# ECE 415/515 –ANALOG INTEGRATED CIRCUIT DESIGN

SHORT CHANNEL BIASING

#### VISHAL SAXENA VSAXENA@UIDAHO.EDU

© Vishal Saxena

### LONG-CHANNEL CMOS, $L_{MIN}$ =1UM

Table 9.1 Typical parameters for analog design using the *long-channel* CMOS process discussed in this book. Note that the parameters may change with temperature or drain-to-source voltage (e.g., Fig. 9.24).

| <i>Long</i> -channel MOSFET parameters for general analog design<br><i>VDD</i> = 5 V and a scale factor of <b>1</b> μ <b>m</b> ( <i>scale</i> = 1e–6) |                             |                             |                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|---------------------------------------------------------|

| Parameter                                                                                                                                             | NMOS                        | PMOS                        | Comments                                                |

| Bias current, $I_D$                                                                                                                                   | 20 µA                       | 20 µA                       | Approximate                                             |

| W/L                                                                                                                                                   | 10/2                        | 30/2                        | Selected based on $I_{D}$ and $V_{{\it DS}, {\it sat}}$ |

| $V_{\rm DS,sat}$ and $V_{\rm SD,sat}$                                                                                                                 | 250 mV                      | 250 mV                      | For sizes listed                                        |

| $V_{\rm GS}$ and $V_{\rm SG}$                                                                                                                         | 1.05 V                      | 1.15 V                      | No body effect                                          |

| $V_{T\!H\!N}{\rm and}V_{T\!H\!P}$                                                                                                                     | 800 mV                      | 900 mV                      | Typical                                                 |

| $\partial V_{THN,P} / \partial T$                                                                                                                     | $-1 \text{ mV/C}^{\circ}$   | $-1.4 \text{ mV/C}^{\circ}$ | Change with temperature                                 |

| $KP_n$ and $KP_p$                                                                                                                                     | $120 \ \mu A/V^2$           | $40 \ \mu A/V^2$            | $t_{ox} = 200 \text{ Å}$                                |

| $C'_{ox} = \varepsilon_{ox}/t_{ox}$                                                                                                                   | $1.75 f \mathrm{F/\mu m^2}$ | $1.75f\mathrm{F/\mu m^2}$   | $C_{ox} = C'_{ox}WL \cdot (scale)^2$                    |

| $C_{oxp}$ and $C_{oxp}$                                                                                                                               | 35 <i>f</i> F               | 105 <i>f</i> F              | PMOS is three times wider                               |

| $C_{\scriptscriptstyle gsn} \text{ and } C_{\scriptscriptstyle sgp}$                                                                                  | 23.3 <i>f</i> F             | 70 <i>f</i> F               | $C_{gs} = \frac{2}{3}C_{ox}$                            |

| $C_{\mathit{gdn}} \text{ and } C_{\mathit{dgp}}$                                                                                                      | 2fF                         | 6 <i>f</i> F                | $C_{gd} = CGDO \cdot W \cdot scale$                     |

| $g_{mn}$ and $g_{mp}$                                                                                                                                 | 150 μA/V                    | 150 μA/V                    | At $I_D = 20 \ \mu A$                                   |

| $r_{on}$ and $r_{op}$                                                                                                                                 | 5 ΜΩ                        | $4 \mathrm{M}\Omega$        | Approximate at $I_D = 20 \ \mu A$                       |

| $g_{mn}r_{on}$ and $g_{mp}r_{op}$                                                                                                                     | 750 V/V                     | 600 V/V                     | Open circuit gain                                       |

| $\lambda_n$ and $\lambda_p$                                                                                                                           | 0.01 V <sup>-1</sup>        | 0.0125 V <sup>-1</sup>      | At <i>L</i> = 2                                         |

| $f_{Tn}$ and $f_{Tp}$                                                                                                                                 | 900 MHz                     | 300 MHz                     | For $L = 2$ , $f_T$ goes up if $L = 1$                  |

fldaho

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

### SHORT-CHANNEL CMOS, $L_{MIN}$ =50NM

Short-channel MOSFET parameters for general analog design VDD = 1 V and a scale factor of 50 nm (scale = 50e-9) Parameter NMOS PMOS Comments Approximate, see Fig. 9.31 Bias current, ID 10 uA 10 uA W/L50/2100/2Selected based on  $I_D$  and  $V_{av}$  $5\mu m/100nm$ Actual W/L 2.5µm/100nm  $L_{min}$  is 50 nm  $V_{DS,sat}$  and  $V_{SD,sat}$ 50 mV50 mVHowever, see Fig. 9.32 and the associated discussion Vom and Vov 70 mV70 mV $V_{GS}$  and  $V_{SG}$ 350 mV350 mVNo body effect 280 mV280 mV Typical V<sub>THN</sub> and V<sub>THP</sub>  $\partial V_{THNP} / \partial T$  $-0.6 \text{ mV/C}^{\circ}$ - 0.6 mV/C° Change with temperature  $110 \ge 10^3 \text{ m/s}$  $90 \ge 10^3 \text{ m/s}$ From the BSIM4 model  $v_{sam}$  and  $v_{sam}$ 14 Å 14 Å Tunnel gate current, 5 A/cm<sup>2</sup> t<sub>ar</sub>  $C'_{ox} = \varepsilon_{ox}/t_{ox}$  $25 f F/\mu m^2$  $25 f F/\mu m^2$  $C_{ox} = C'_{ox}WL \cdot (scale)^2$ PMOS is two times wider  $C_{oxp}$  and  $C_{oxp}$ 6.25 f F 12.5 f F  $C_{gs} = \frac{2}{3}C_{ox}$ C\_m and C\_sep 4.17 fF 8.34 fF  $C_{gd} = CGDO \cdot W \cdot scale$ 1.56 f F 3.7*f* F  $C_{adm}$  and  $C_{dem}$  $150 \ \mu A/V$  $g_{mn}$  and  $g_{mp}$ 150 µA/V At  $I_D = 10 \ \mu A$ 167 kΩ 333 kΩ Approximate at  $I_D = 10 \ \mu A$ ron and rov 25 V/V 50 V/V !!Open circuit gain!! gmmron and gmprov  $0.6 V^{-1}$  $0.3 V^{-1}$ L = 2 $\lambda_n$  and  $\lambda_n$  $f_{T_n}$  and  $f_{T_n}$ 6000 MHz 3000 MHz Approximate at L = 2

Table 9.2 Typical parameters for analog design using the *short-channel* CMOS process discussed in this book. These parameters are valid only for the device sizes and currents listed.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

#### © Vishal Saxena

# BMR CIRCUIT IN 1UM CMOS

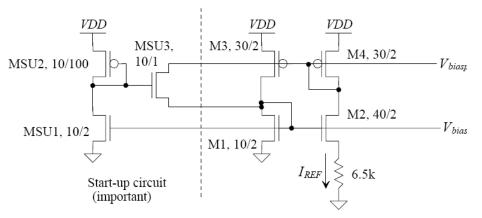

Figure 20.15 Beta-multiplier reference for biasing in the long-channel process described in Table 9.1.

Figure 20.16 The reference currents through M1 and M2 in the Beta-multiplier.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Ι

© Vishal Saxena

## **50NM BMR CIRCUIT**

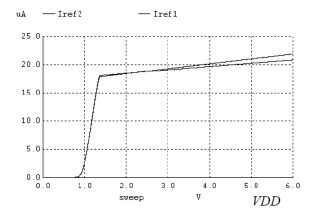

Figure 20.18 Beta-multiplier reference for short-channel design (see Table 9.2).

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

#### © Vishal Saxena

## SHORT-CHANNEL BMR CIRCUIT

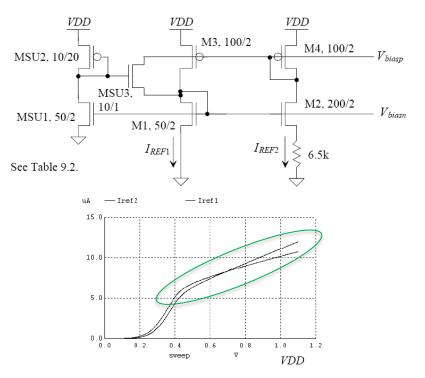

Figure 20.19 Increasing the output resistance of short-channel MOSFETs using feedback. The result, for the Beta-multiplier circuit, is better power supply sensitivity.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

][

C Vishal Saxena

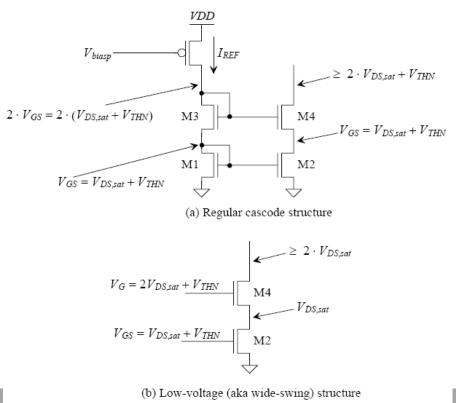

## **CASCODE CURRENT SOURCES**

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figure 20.31 DC voltages in (a) a cascode current mirror and in (b) a low-voltage cascode.

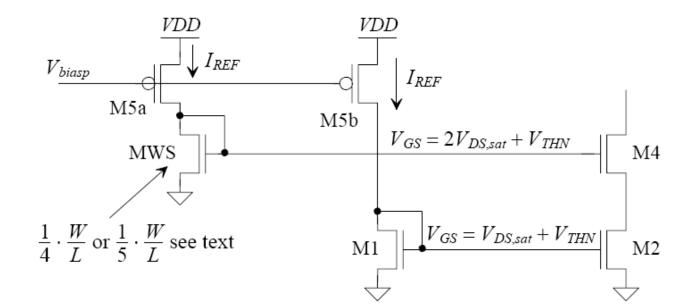

## WIDE-SWING CASCODE CURRENT SOURCES

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figure 20.32 Generating a bias voltage for M4.

© Vishal Saxena

## WIDE-SWING CASCODE CURRENT SOURCES

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figure 20.33 Wide-swing cascode current source in the long-channel process.

© Vishal Saxena

College of Engineering

<u>Oniversity or idaho</u>

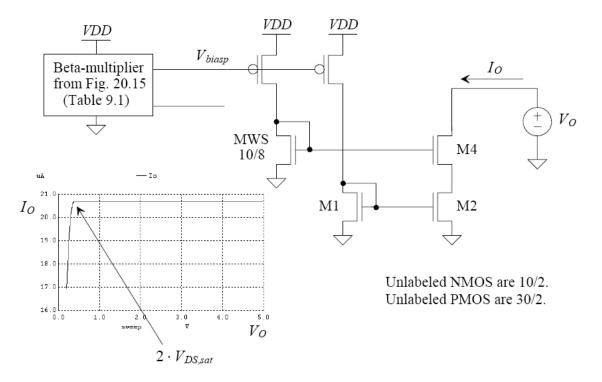

### LONG-CHANNEL BIAS CIRCUITS

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

/ishal S

Figure 20.43 General biasing circuit for long-channel CMOS design using the data in Table 9.1

yof Idaho

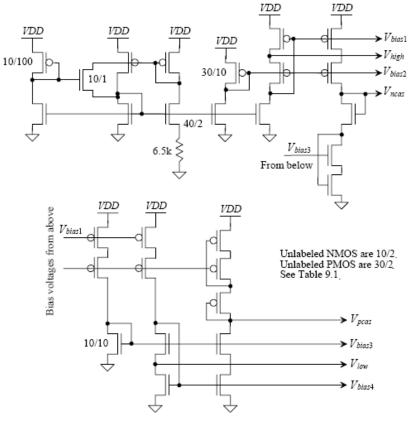

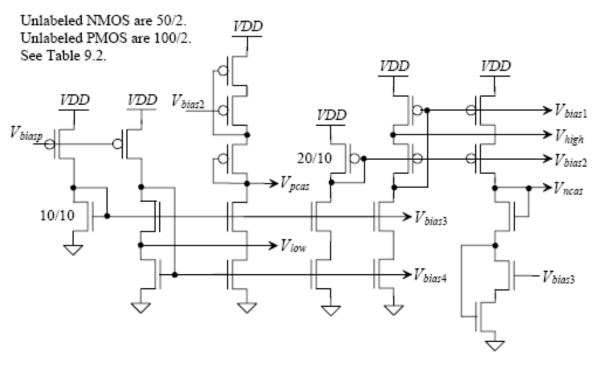

#### SHORT-CHANNEL BIAS CIRCUITS

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figure 20.47 General biasing circuit for short-channel design using the data in Table 9.2.

#### © Vishal Saxena

College of Engineering

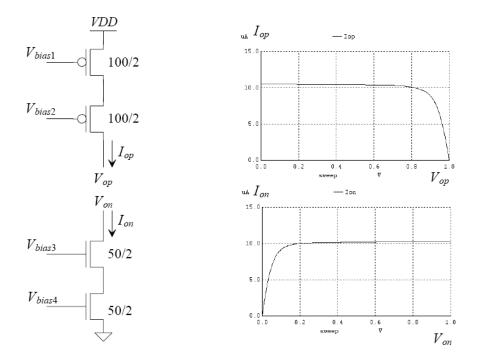

### **USING BIAS REFERENCES**

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Bias voltages come from Fig. 20.47 (short-channel parameters in Table 9.2).

Figure 20.48 Cascode current sources operating in a short-channel process.

#### © Vishal Saxena