# ECE 415/515 –ANALOG INTEGRATED CIRCUIT DESIGN

#### CMOS PROCESS CHARACTERIZATION

VISHAL SAXENA VSAXENA@UIDAHO.EDU

© Vishal Saxena

#### **DESIGN PARAMETERS**

- Analog circuit designers care about:

- Open-loop Gain: g<sub>m</sub>r<sub>o</sub>

- Bandwidth (speed):  $C_{gs}$ ,  $C_{gd}$ ,  $f_{T}$ ,  $f_{max}$ , etc.

- Power: V<sub>DD</sub>\*I<sub>DD</sub>

- Voltage swing: V<sub>DS,sat</sub>

- Noise

- Linearity

- Mismatch (systematic and random)

- Layout Engineers care about:

- W/L sizing, layout matching, circuit isolation,....

## SHORT CHANNEL CHARACTERISTICS

- Square law equations are no longer valid

- Intuition derived from classical analysis is still helpful

- $i_D = v_{sat}WC_{ox}(V_{GS}-V_{THN}-V_{DS,sat})$

- v<sub>sat</sub>=saturation velocity

- Cox=oxide capacitance per unit area

- Velocity saturation and overshoot effects

- Current analog technology is 14nm, typical designs in 65nm

- Requires NDA agreements

- CMOS Book uses 50nm process parameters

- V<sub>DD</sub>=1V, L<sub>min</sub>=50nm

- V<sub>THN</sub>=V<sub>THP</sub>=280mV

## SHORT CHANNEL CHARACTERISTICS (2)

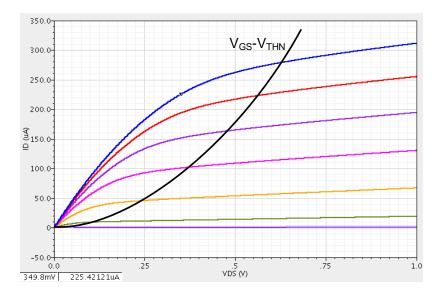

- Short-channel devices appear to enter saturation as a lower voltage than predicted by the equation  $V_{DS,sat}=V_{GS}-V_{THN}$

- $V_{DS,sat} \neq V_{ov} = V_{GS} V_{THN}$

- The actual inversion layer charge distribution,  $Q'_{I}(y)$ , is a function of  $V_{DS}$ , in addition to  $V_{GS}$

- $Q_{I}^{'}(y)$  becomes zero at a lower  $V_{DS,sat}$

## SHORT CHANNEL CHARACTERISTICS (3)

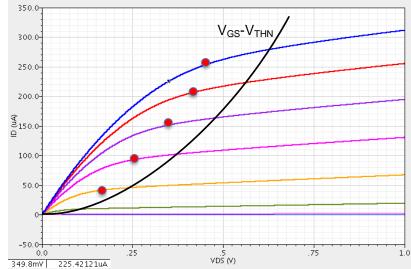

- Is a large range for the saturation region beneficial?

- We could really use the larger swing!

- Not really, need to look at the region where r<sub>o</sub> is large and that occurs when the device is deep into saturation :(

#### THRESHOLD VOLTAGE

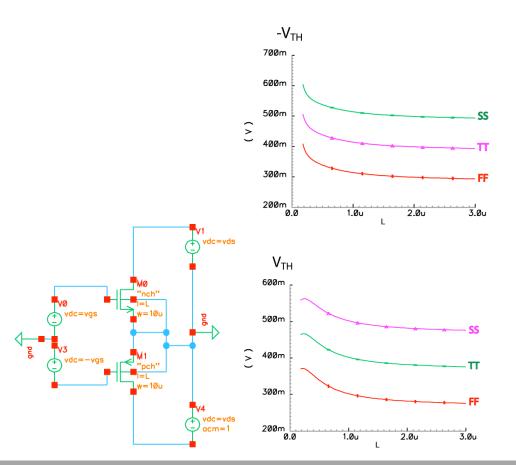

- Strong function of L

- Use long channel for V<sub>TH</sub> matching

- Process variations

- Run-to-run ~100mV

- Slow/nominal/fast

- Good design should be insensitive to the absolute value of  $V_{TH}$

- Should only depend upon the mismatch in V<sub>TH</sub> (~1mV) for good layout and large devices

University of Idaho College of Engineering

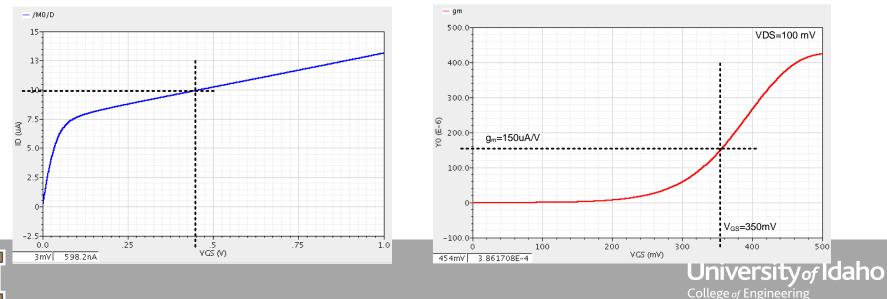

## SHORT CHANNEL CHARACTERISTICS

- For short-channel design, the equation  $V_{DS,sat}=V_{GS}-V_{THN}$  is meaningless

- From now onwards, we'll talk in terms of the gate overdrive voltage

- $V_{ov} = V_{GS} V_{THN} > V_{DS,sat}$

- We can use  $V_{ov} = 5\%$  of  $V_{DD}$  as a starting point for high-speed design (build your intuition)

- Vov = 70mV!

- VGS = 350mV

- A more robust method is to use constant  $g_m/I_D$  and current density ( $I_D/W$ ) across the design, instead of a constant  $V_{ov}$

- Refer to the slides "Analog Design Using  $g_m/I_d$  and  $f_t$  Metrics" by Prof. Boser of UC Berkeley

University of Idaho

College of Engineering

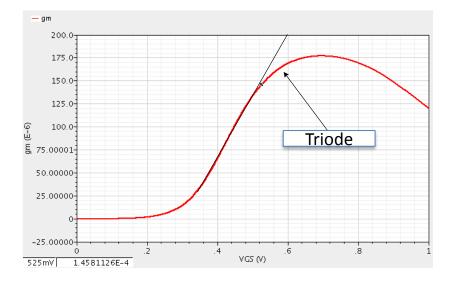

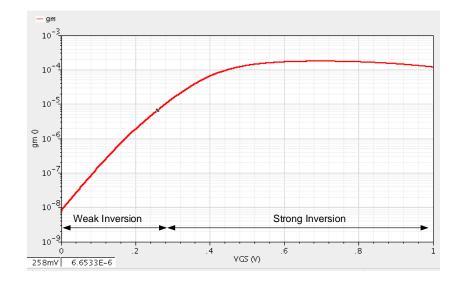

#### TRANSCONDUCTANCE

$g_m = (V_{GS} - V_{THN})$

gmsub-VT=ID/NVT

#### TRANSCONDUCTANCE

- Given  $V_{ov}=2I_D/g_m$ , and a specified value of  $g_m$

- Pick I<sub>D</sub> and W based on

- Here, for a  $g_m$ =150uA/V, we pick 10uA for sufficient current drive

- This leads to W=50 for NMOS and W=100 for PMOS

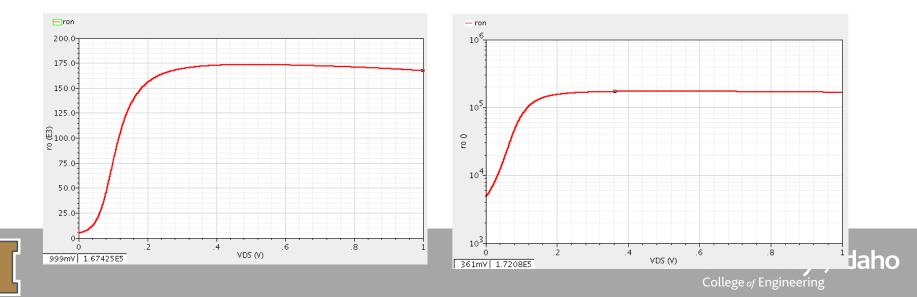

#### **OUTPUT RESISTANCE**

- To determine  $V_{DS,sat}$ , look at the point where the output resistance starts to increase (Here,  $V_{DS,sat} = 50mV$ )

- We get considerably higher output resistances at a larger VDS(important!)

Can't just model by a simple equation,  $r_o = 1/I_{D,sat}$

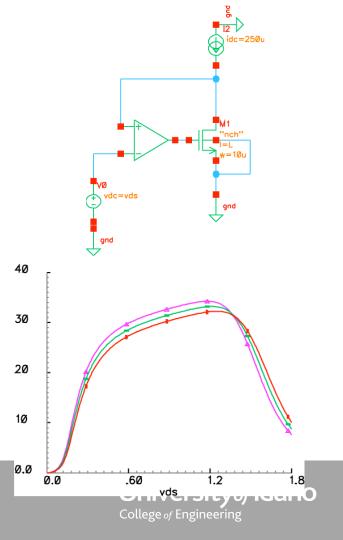

# **OPEN-LOOP GAIN** $(g_m r_o)$

- g<sub>m</sub>r<sub>o</sub> is more useful than just r<sub>o</sub>

- Represents maximum attainable gain from a transistor

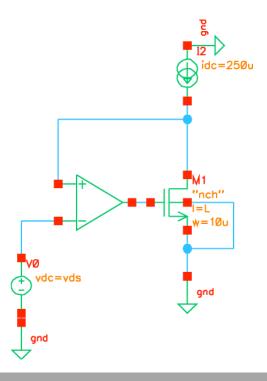

- Simulation Notes:

- Bias current *idc* sets V<sub>ov</sub>

- Use feedback to find the correct  $V_{GS}$  while sweeping  $V_{DS}$

- Use relatively small error-amplifier gain (A=100) for fast DC convergence

# **OPEN-LOOP GAIN** $(g_m r_o)$

- The open loop gain is roughly  $g_m r_o = 150 \mu AV \cdot 170 k$ ~25

- Considerably lower than the open-loop gain in a long-channel process.

University of Idaho College of Engineering

#### LONG-CHANNEL CMOS, $L_{MIN}$ =1UM

Table 9.1 Typical parameters for analog design using the *long-channel* CMOS process discussed in this book. Note that the parameters may change with temperature or drain-to-source voltage (e.g., Fig. 9.24).

| <i>Long</i> -channel MOSFET parameters for general analog design<br><i>VDD</i> = 5 V and a scale factor of <b>1</b> μ <b>m</b> ( <i>scale</i> = 1e–6) |                             |                             |                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|----------------------------------------------------|

| Parameter                                                                                                                                             | NMOS                        | PMOS                        | Comments                                           |

| Bias current, $I_D$                                                                                                                                   | 20 µA                       | 20 µA                       | Approximate                                        |

| W/L                                                                                                                                                   | 10/2                        | 30/2                        | Selected based on $I_{\rm D}$ and $V_{\rm DS,sat}$ |

| $V_{\rm DS,sat}$ and $V_{\rm SD,sat}$                                                                                                                 | 250 mV                      | 250 mV                      | For sizes listed                                   |

| $V_{GS}$ and $V_{SG}$                                                                                                                                 | 1.05 V                      | 1.15 V                      | No body effect                                     |

| $V_{T\!H\!N}  {\rm and}   V_{T\!H\!P}$                                                                                                                | 800 mV                      | 900 mV                      | Typical                                            |

| $\partial V_{THN,P} / \partial T$                                                                                                                     | $-1 \text{ mV/C}^{\circ}$   | $-1.4 \text{ mV/C}^{\circ}$ | Change with temperature                            |

| $KP_n$ and $KP_p$                                                                                                                                     | $120 \ \mu A/V^2$           | $40 \ \mu A/V^2$            | $t_{ox} = 200 \text{ Å}$                           |

| $C'_{ox} = \varepsilon_{ox}/t_{ox}$                                                                                                                   | $1.75 f \mathrm{F/\mu m^2}$ | $1.75f\mathrm{F/\mu m^2}$   | $C_{ox} = C'_{ox}WL \cdot (scale)^2$               |

| $C_{oxn}$ and $C_{oxp}$                                                                                                                               | 35 <i>f</i> F               | 105 <i>f</i> F              | PMOS is three times wider                          |

| $C_{\scriptscriptstyle gsn} \text{ and } C_{\scriptscriptstyle sgp}$                                                                                  | 23.3 <i>f</i> F             | 70 <i>f</i> F               | $C_{gs} = \frac{2}{3}C_{ox}$                       |

| $C_{\mathit{gdn}} \text{ and } C_{\mathit{dgp}}$                                                                                                      | 2fF                         | 6 <i>f</i> F                | $C_{gd} = CGDO \cdot W \cdot scale$                |

| $g_{mn}$ and $g_{mp}$                                                                                                                                 | 150 µA/V                    | 150 μA/V                    | At $I_D = 20 \ \mu A$                              |

| $r_{on}$ and $r_{op}$                                                                                                                                 | 5 ΜΩ                        | 4 MΩ                        | Approximate at $I_D = 20 \ \mu A$                  |

| $g_{mn}r_{on}$ and $g_{mp}r_{op}$                                                                                                                     | 750 V/V                     | 600 V/V                     | Open circuit gain                                  |

| $\lambda_n$ and $\lambda_p$                                                                                                                           | 0.01 V <sup>-1</sup>        | $0.0125 \text{ V}^{-1}$     | At <i>L</i> = 2                                    |

| $f_{Tn}$ and $f_{Tp}$                                                                                                                                 | 900 MHz                     | 300 MHz                     | For $L = 2$ , $f_T$ goes up if $L = 1$             |

fldaho

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

#### SHORT-CHANNEL CMOS, $L_{MIN}$ =50NM

Short-channel MOSFET parameters for general analog design VDD = 1 V and a scale factor of 50 nm (scale = 50e-9) Parameter NMOS PMOS Comments Approximate, see Fig. 9.31 Bias current, ID 10 uA 10 uA W/L50/2100/2Selected based on  $I_D$  and  $V_{av}$  $5\mu m/100nm$ Actual W/L 2.5µm/100nm  $L_{min}$  is 50 nm  $V_{DS,sat}$  and  $V_{SD,sat}$ 50 mV50 mVHowever, see Fig. 9.32 and the associated discussion Vom and Vov 70 mV70 mV $V_{GS}$  and  $V_{SG}$ 350 mV350 mVNo body effect 280 mV280 mV Typical V<sub>THN</sub> and V<sub>THP</sub>  $\partial V_{THNP} / \partial T$  $-0.6 \text{ mV/C}^{\circ}$ - 0.6 mV/C° Change with temperature  $110 \ge 10^3 \text{ m/s}$  $90 \ge 10^3 \text{ m/s}$ From the BSIM4 model  $v_{sam}$  and  $v_{sam}$ 14 Å 14 Å Tunnel gate current, 5 A/cm<sup>2</sup> t<sub>ar</sub>  $C'_{ox} = \varepsilon_{ox}/t_{ox}$  $25 f F/\mu m^2$  $25 f F/\mu m^2$  $C_{ox} = C'_{ox}WL \cdot (scale)^2$ PMOS is two times wider  $C_{oxp}$  and  $C_{oxp}$ 6.25 f F 12.5 f F  $C_{gs} = \frac{2}{3}C_{ox}$ C\_m and C\_sep 4.17 fF 8.34 fF  $C_{gd} = CGDO \cdot W \cdot scale$ 1.56 f F 3.7*f* F  $C_{edn}$  and  $C_{den}$  $150 \ \mu A/V$  $g_{mn}$  and  $g_{mp}$ 150 µA/V At  $I_D = 10 \ \mu A$ 167 kΩ 333 kΩ Approximate at  $I_D = 10 \ \mu A$ ron and rov 25 V/V 50 V/V !!Open circuit gain!! gmmron and gmprov  $0.6 V^{-1}$  $0.3 V^{-1}$ L = 2 $\lambda_n$  and  $\lambda_n$  $f_{T_n}$  and  $f_{T_n}$ 6000 MHz 3000 MHz Approximate at L = 2

Table 9.2 Typical parameters for analog design using the *short-channel* CMOS process discussed in this book. These parameters are valid only for the device sizes and currents listed.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

#### © Vishal Saxena

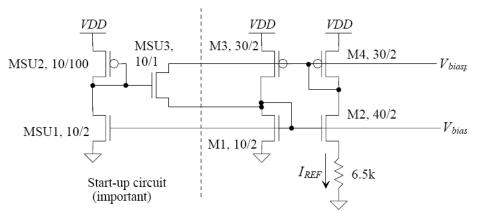

## BMR CIRCUIT IN 1UM CMOS

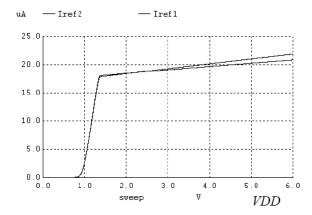

Figure 20.15 Beta-multiplier reference for biasing in the long-channel process described in Table 9.1.

Figure 20.16 The reference currents through M1 and M2 in the Beta-multiplier.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Γ

© Vishal Saxena

University of Idaho College of Engineering