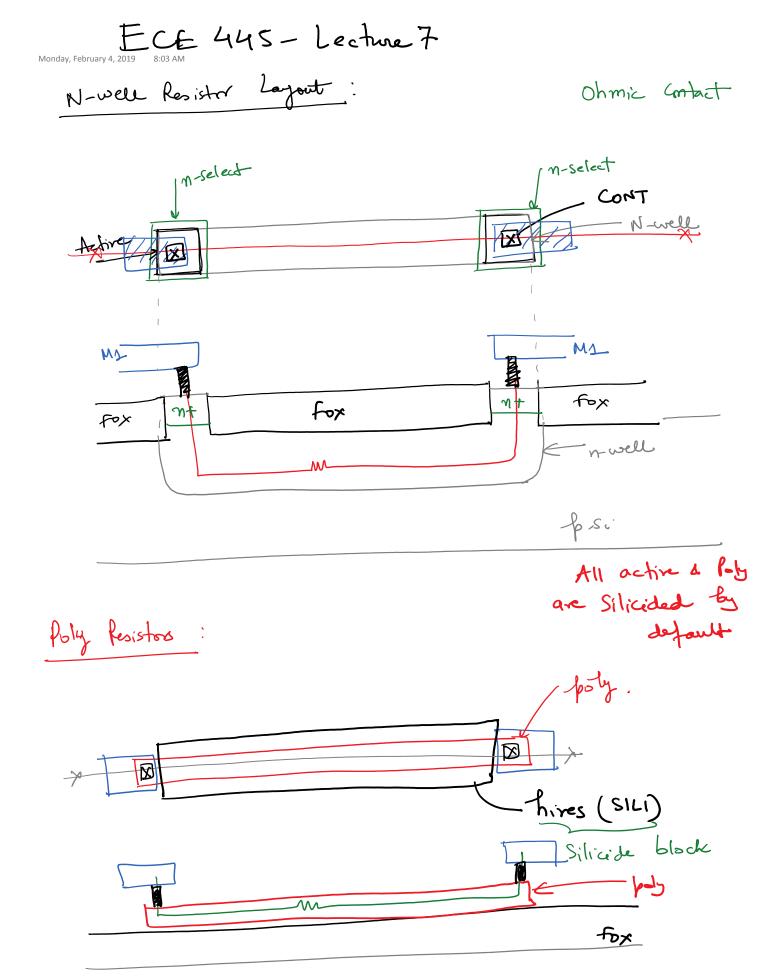

f-si 20 Con alse dope polysilicon using n-select or p-select

Monday, February 4, 2019 8:19 AM

## Monday, February 4, 2019 8:25 AM

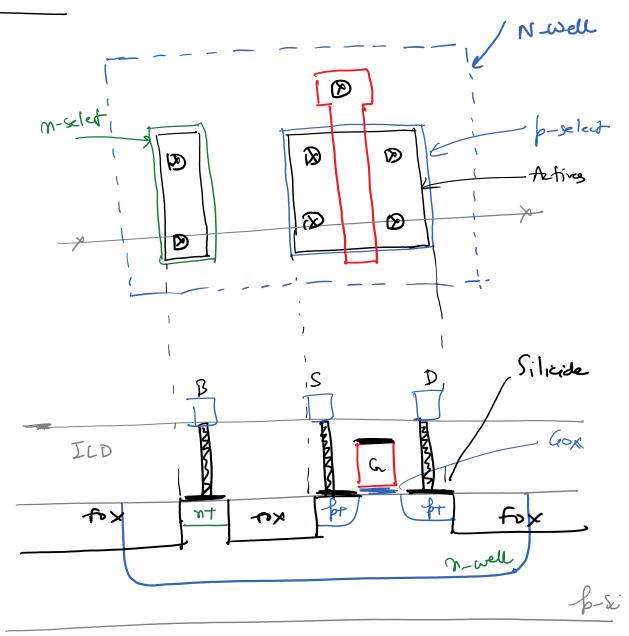

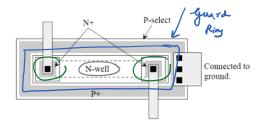

Figure 5.5 Guard ringing an n-well resistor.

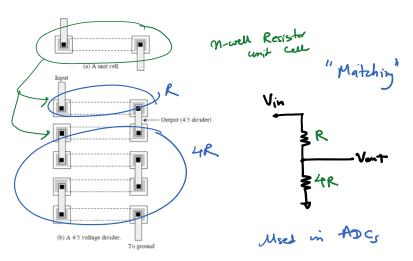

Figure 5.4 (a) Layout of a unit resistor cell, and (b) layout of a divider.

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

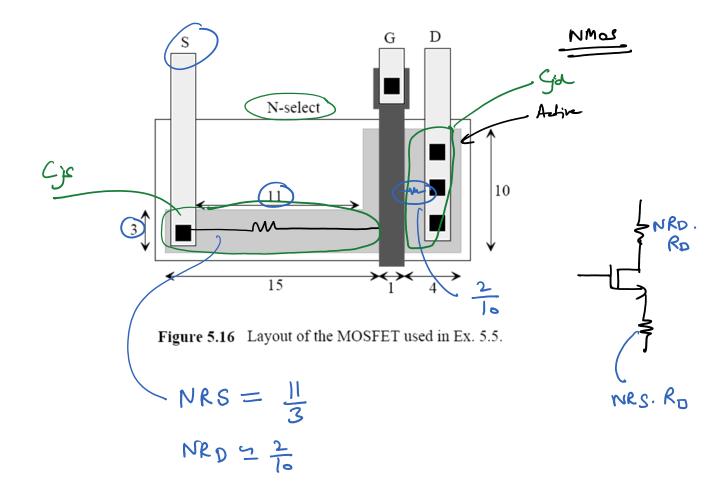

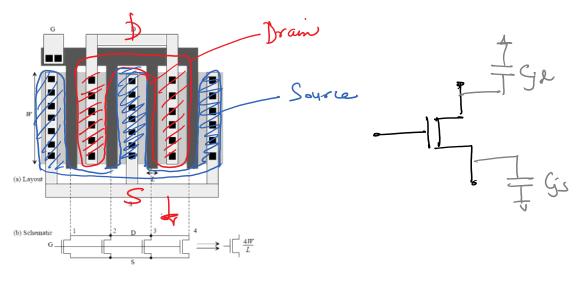

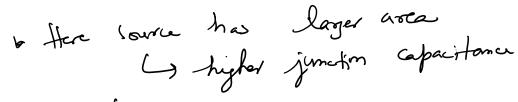

Junction Capacitance

Gis & As =

$$15 \times 2 = 45$$

(Giber unit

area)

Gis & Ps =  $((5+3) \times 2$

Spice instance:

M<sub>1</sub> D & S B L=1 W=10 AD=40 As= 45

PD = 28 PS= 24 NRD=0 NRS=47

for 15 cms scale = 0.3 jum

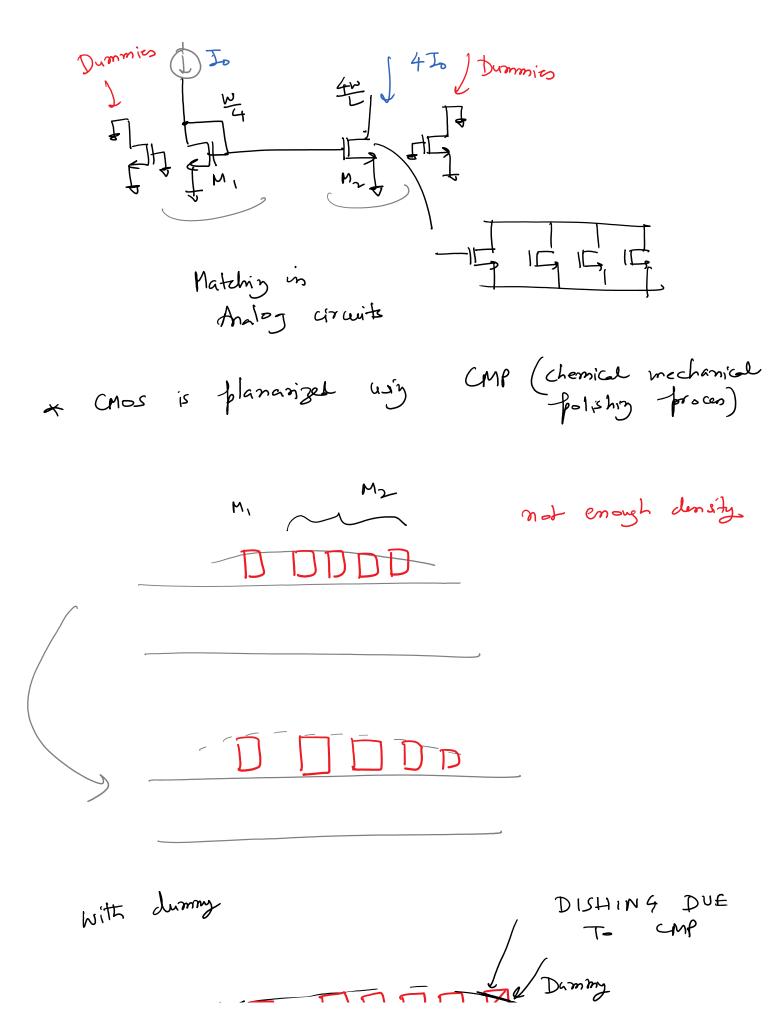

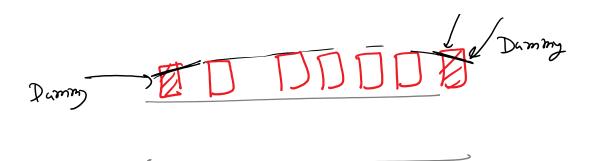

Monday, February 4, 2019 8:35 AM

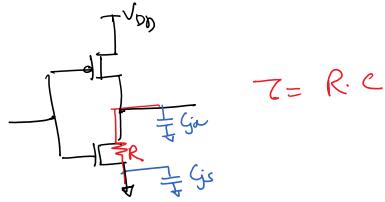

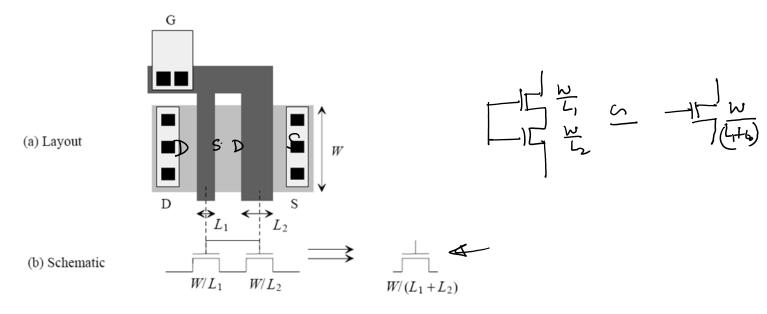

$$\frac{W}{L} = \frac{10 \times \text{scde}}{2 \times \text{scde}} \qquad \qquad =) \qquad \frac{W}{L} = \frac{5 \times 0}{2} \qquad \qquad \text{layout}$$

$$\frac{W}{L} = \frac{3 \times 0}{2} \qquad \qquad \text{layout}$$

$$\frac{W}{L} = \frac{3 \times 0}{2} \qquad \qquad \text{layout}$$

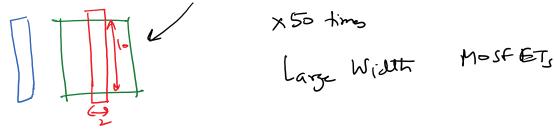

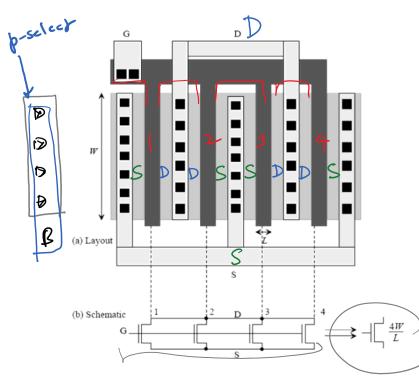

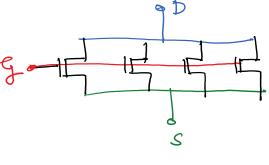

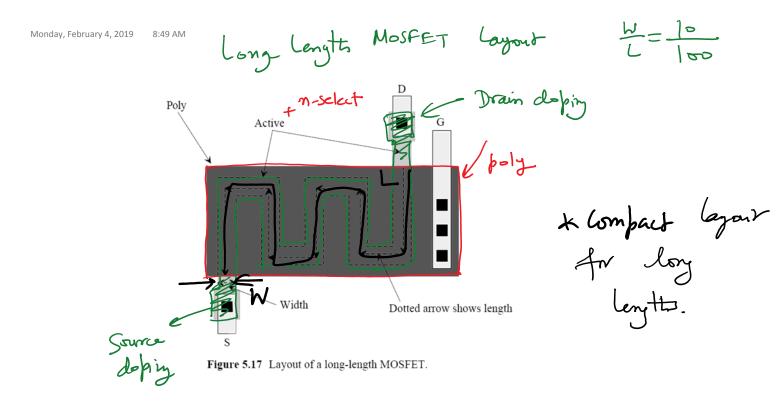

Figure 5.18 Layout and equivalent schematic of a large-width MOSFET.

New Section 1 Page 8

Figures from CMOS Circuit Design, Layout, and Simulation, Copyright Wiley-IEEE, CMOSedu.com

Figure 5.18 Layout and equivalent schematic of a large-width MOSFET.

Constituenter She want larger of the capacitances to be discharged to ground with small switch resistance

Figure 5.19 MOSFETs in series with gates tied together behave as a single MOSFET with the sum of the lengths.

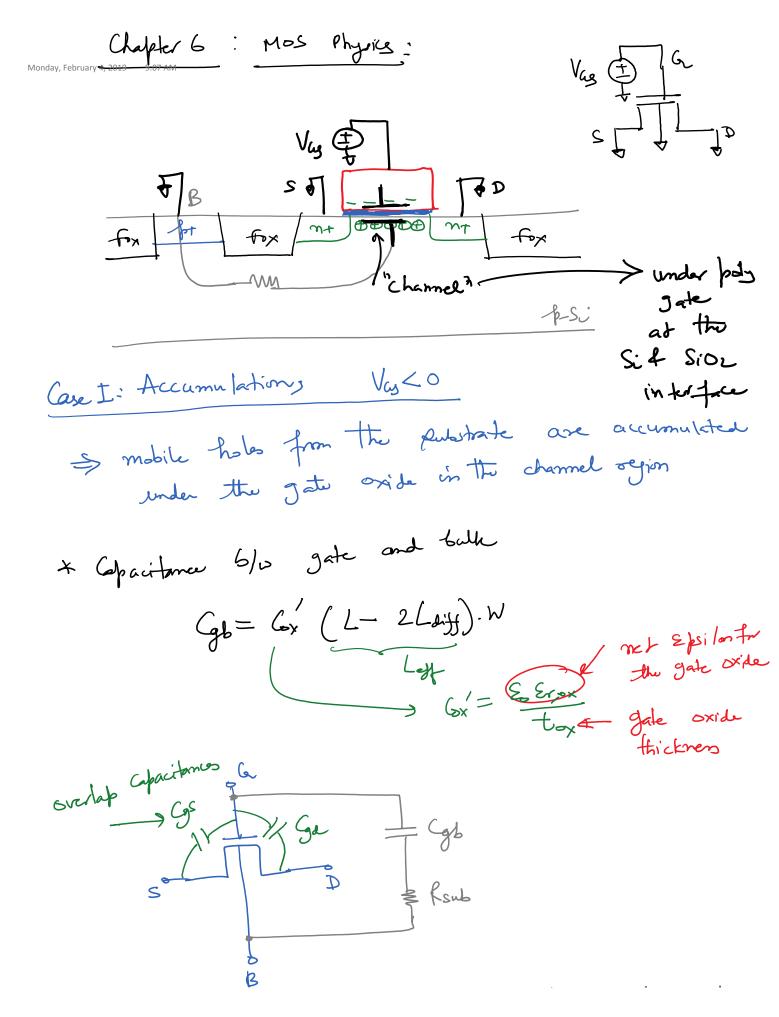

\* MOSFET in Accumulation froms ~ poor quality capictor due to the series resistance.