apacitance.

.

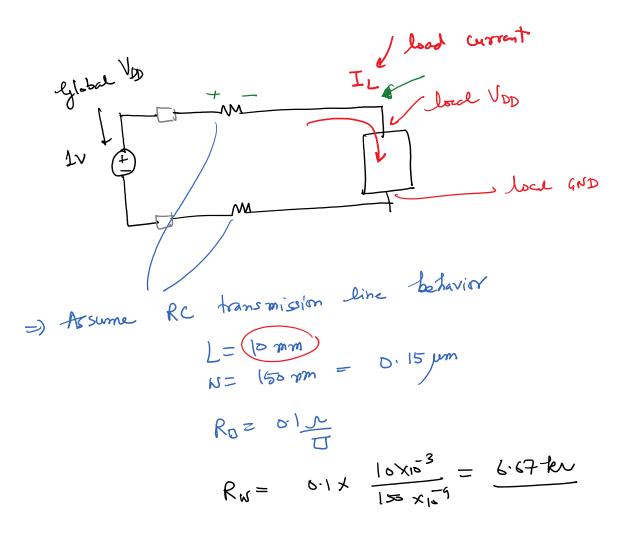

DC:

$$I_L = 50 \mu A$$

$\log V_{DD} = V_{DD,L} = V_{DD} - I_L \cdot R_W = 667 mV$

$\log V_{DD} = V_{DD,L} = 0 + I_L \cdot R_W = 333 mV$

$\log V_{DD} = 0 + I_L \cdot R_W = 333 mV$

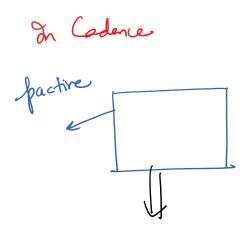

Monday, January 28, 2019 8:35 AM

Monday, January 28, 2019

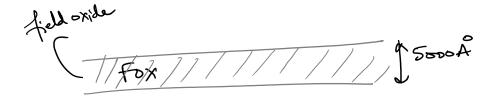

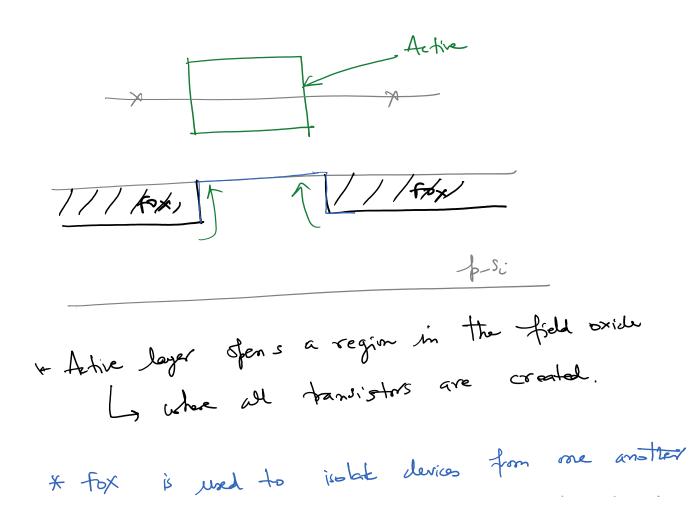

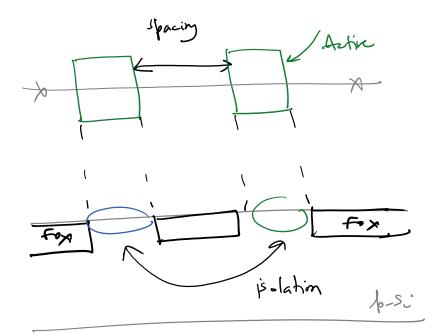

8:47 AM Chapter 4 : Active Layers

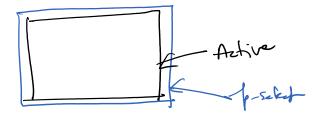

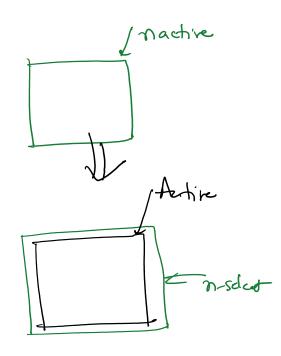

"Active Layer"

n-well M2, M2, M3. --. Via1,2 glars

Ly thich enough to keep interaction of adjacent areas to a minimum.

Monday, January 28, 2019 8:54 AM

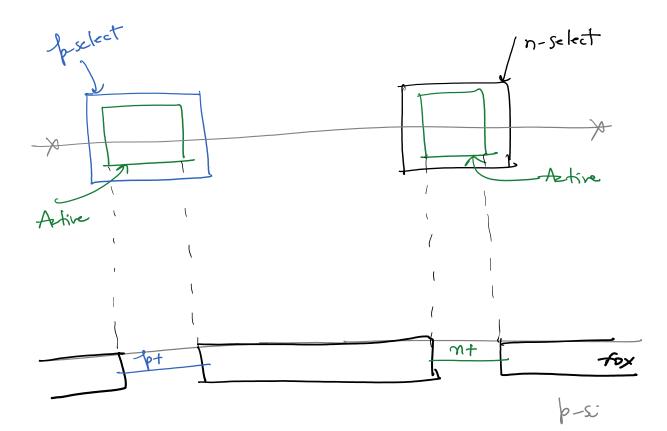

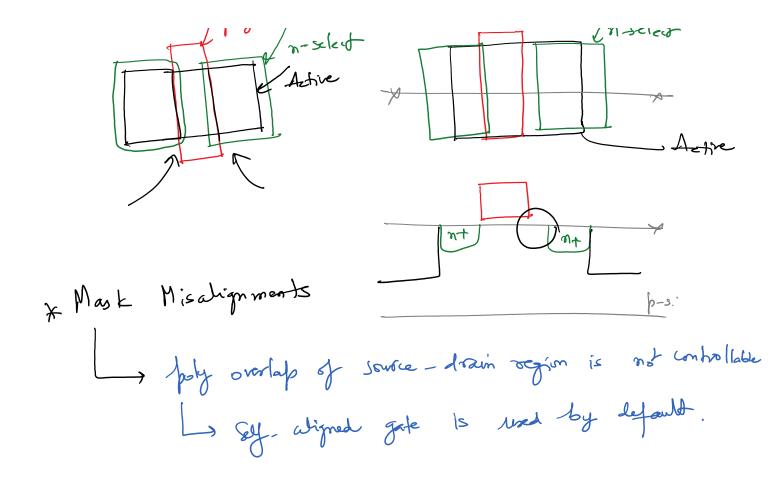

for and no select layors .

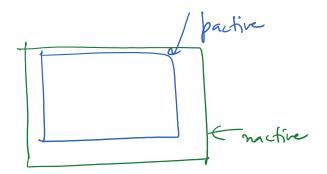

Monday, January 28, 2019 9:00 AM polysilian layer à una for MOSFET formation Poly Lager: Ly "Poly" acts as a 'mark" for the drain source implants. poly -Active - n-seket × m-implant Gale Oxide (gox) n-+ ME -fox for \$-5-& Self-aligned gate process. > Poly on Active >> MOSFET ] Problem Layout / boby / n-select In-seles

\* July can be used like a wine for Auting. Ly poly and active regions are "Silicided" by default. Silicide => Cobalt or Tunesten + Silicon/Julysilicon

poly