gake Delay > 3

Achire > 3<sup>2</sup> 4 Supply woltage

Achire > 3<sup>3</sup> 4

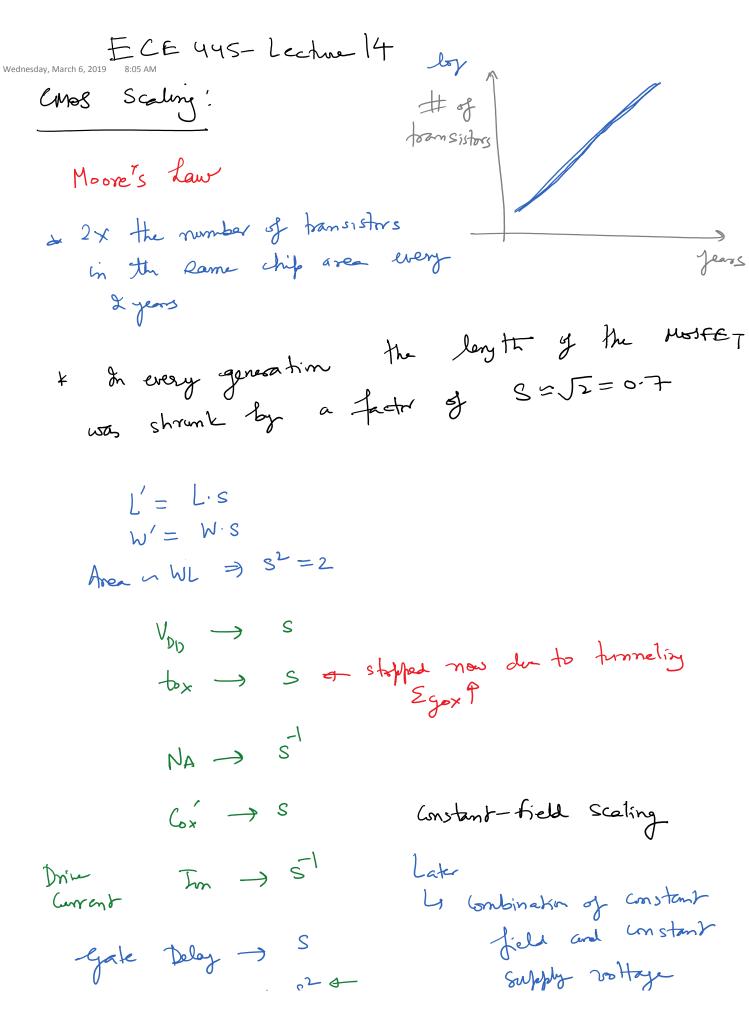

Scaling.

The lower | 50 mm > 0.18 mm > 0.18 mm > 130 mm

Now | 10 mm | 4 = 22 = 32 = 45 mm = 65 mm = 90 mm = 10 mm

ARM

Chapter lo Wednesday, March 6, 2019 8:28 AM

## Models for Digital Design:

\* Triple Well frown

Scallering due to

November of the November of

SoI

Si phos 1 Amos Bulk Oxide

Box

Box

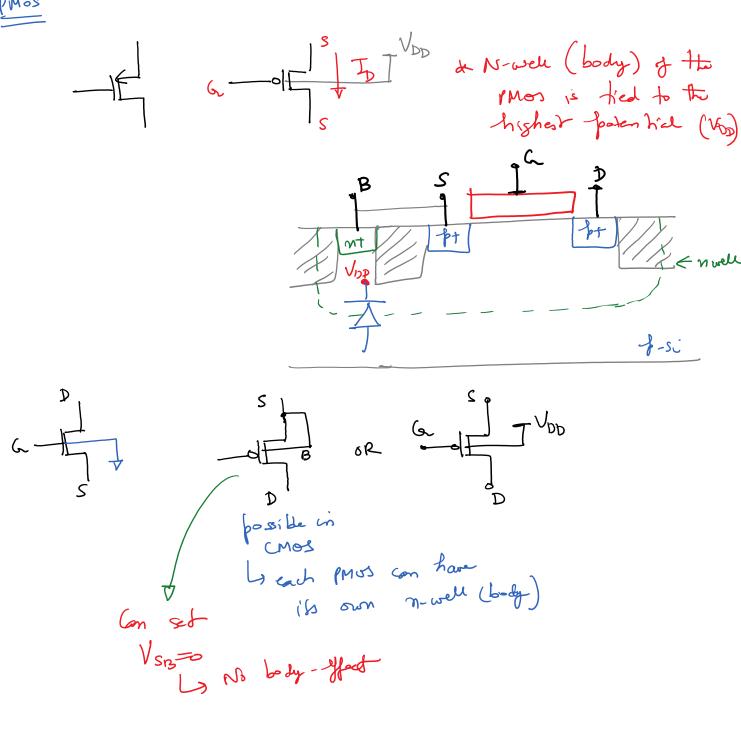

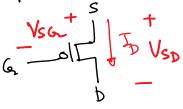

PMOS => All fositive

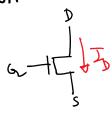

NMOS

VDS, sat = Vas-VTHN

Va> Vsa  $V_{DS} \rightarrow V_{SD}$  VIA

VCD Vsa L Varel

TD = | WSU-VAHP) VSD - VSD | VSD | VSD | VSD | VSD | VSD | VSD Straken

$V_{SD} < V_{Sp}$  sar =  $V_{Sp} < V_{Sp}$

Veatry

In this convention Vitte 4 To are fasilitie.

$$V_{SQ} + V_{SQ} + V_{SQ} = V$$

$$g_n = 0$$

$= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$   $= 0$

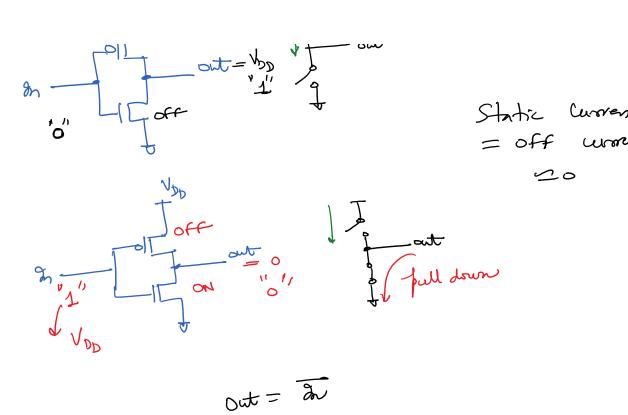

NMOS+ PMOS = CMOS

Complementary Mos

\* Complementary Logic

NMos-only logic

The static current to

Solvent to

Vont of very gam your Vin

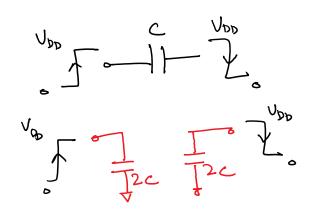

## Miller Capacitance

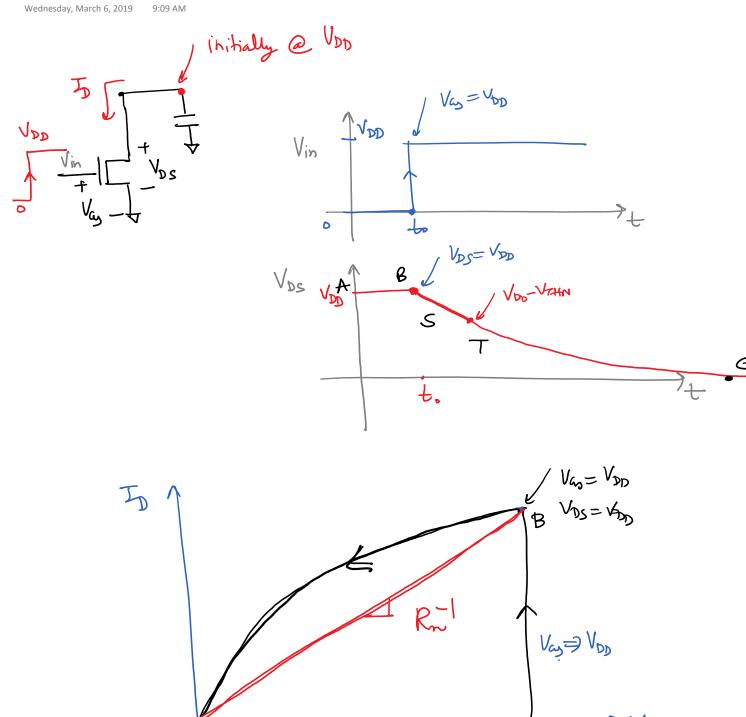

before switching:

After switching?

met change

\* charge supplied by the source = 2CVDD

Effective input apacitance =

$$\frac{Da}{V_{DD}} = \frac{2CV_{DD}}{V_{DD}} = 2C$$

\* change Sink by the

In general

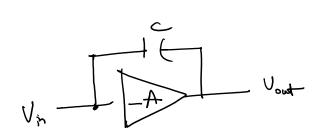

& Miller Effect -> Capacitance Multiplication Effect

for an inverter, gain = -1 Cin=2C

Cod=2

New Section 1 Page 9

Cin=AC

parasitic capacitances

C= Gunt Gup is the Milker Capacitance

Capacitance

Capacitance

Cyclin Gup

Capacitance

VDSTO