# Clocked Circuits Additional Slides

### Vishal Saxena ECE, Boise State University

Nov 30, 2010

Vishal Saxena | CMOS Inverter

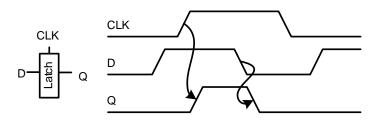

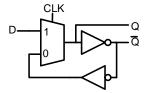

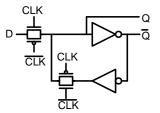

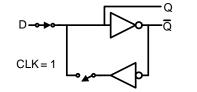

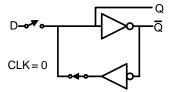

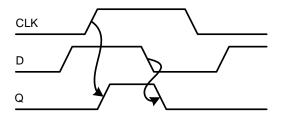

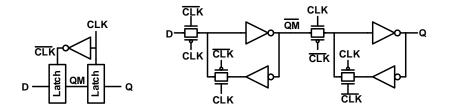

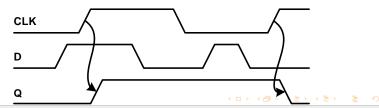

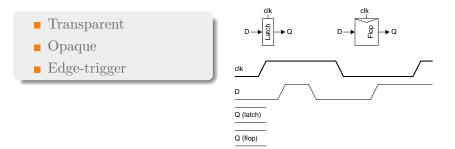

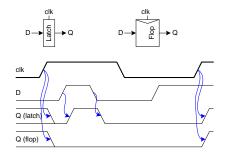

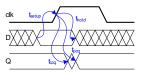

### • When CLK = 1, latch is transparent

- D flows through to Q like a buffer

- When CLK = 0, the latch is opaque

Q holds its old value independent of D

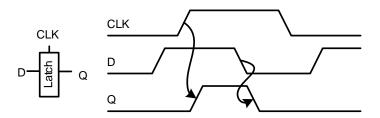

- When CLK = 1, latch is transparent

- D flows through to Q like a buffer

- When CLK = 0, the latch is opaque

Q holds its old value independent of D

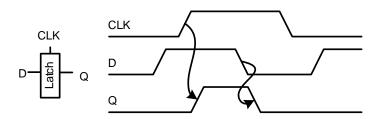

- When CLK = 1, latch is transparent

- D flows through to Q like a buffer

- When CLK = 0, the latch is opaque

Q holds its old value independent of D

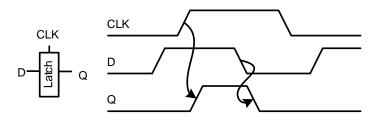

- When CLK = 1, latch is transparent

- D flows through to Q like a buffer

- When CLK = 0, the latch is opaque

- Q holds its old value independent of D

### Multiplexer chooses D or old Q

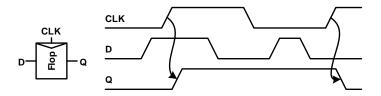

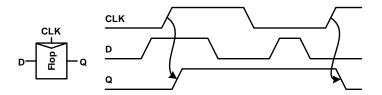

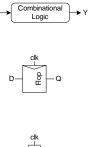

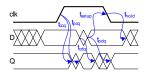

### ■ When CLK rises, D is copied to Q

• At all other times, Q holds its value

a.k.a. positive edge-triggered flip-flop, master-slave flip-flop

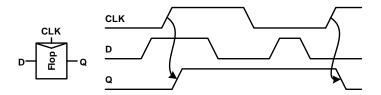

### ■ When CLK rises, D is copied to Q

• At all other times, Q holds its value

a.k.a. positive edge-triggered flip-flop, master-slave flip-flop

### ■ When CLK rises, D is copied to Q

• At all other times, Q holds its value

a.k.a. positive edge-triggered flip-flop, master-slave flip-flop

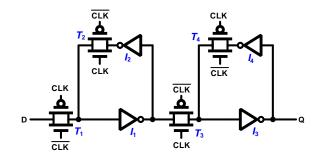

### Built from master and slave D latches

# D Flip-flop Operation

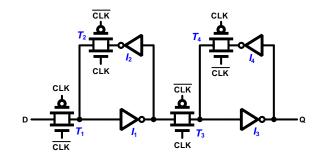

$$\bullet t_{setup} = t_{T_1} + t_{I_1}$$

$$\bullet t_{hold} = -(t_{T_1} + t_{I_1})$$

$$\bullet t_{pcq} = t_{T_3} + t_{I_3}$$

### Vishal Saxena | CMOS Inverter

$$\bullet t_{setup} = t_{T_1} + t_{I_1}$$

$$\bullet t_{hold} = -(t_{T_1} + t_{l_1})$$

$$\bullet t_{pcq} = t_{T_3} + t_{I_3}$$

•

$$t_{setup} = t_{T_1} + t_{I_1}$$

•  $t_{hold} = -(t_{T_1} + t_{I_1})$

•  $t_{nca} = t_{T_2} + t_{I_2}$

•

$$t_{setup} = t_{T_1} + t_{I_1}$$

•  $t_{hold} = -(t_{T_1} + t_{I_1})$

•  $t_{nca} = t_{T_2} + t_{I_2}$

•

$$t_{setup} = t_{T_1} + t_{l_1}$$

•  $t_{hold} = -(t_{T_1} + t_{l_1})$

•  $t_{pcq} = t_{T_3} + t_{l_3}$

### Vishal Saxena | CMOS Inverter

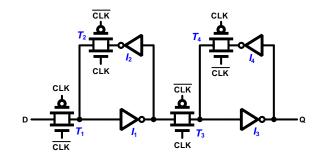

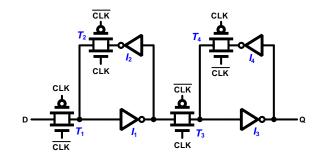

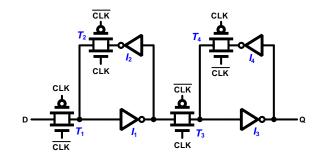

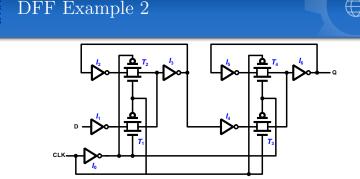

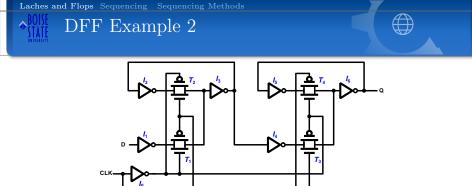

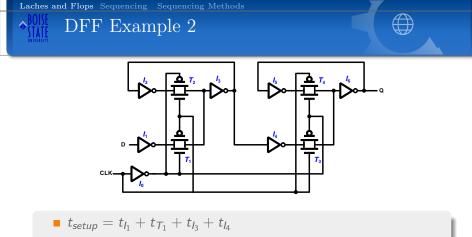

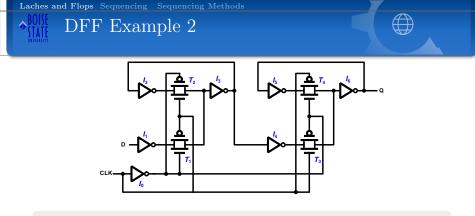

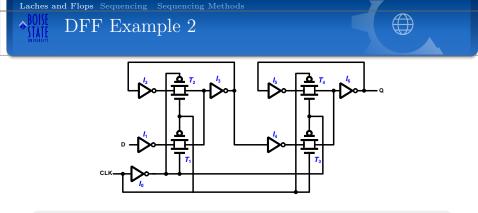

$$t_{setup} = t_{I_1} + t_{T_1} + t_{I_3} + t_{I_4}$$

•  $t_{hold} = t_{I_0} - (t_{I_1} + t_{T_1} + t_{I_3})$  (Note that the  $\overline{CLK}$  and CLK have an overlap equal to an inverter delay  $(t_{I_0})$ )

Need to hold input (D), otherwise the master will latch new D value.

$$\bullet t_{pcq} = t_{T_3} + t_{I_6}$$

$$t_{setup} = t_{I_1} + t_{T_1} + t_{I_3} + t_{I_4}$$

•  $t_{hold} = t_{I_0} - (t_{I_1} + t_{T_1} + t_{I_3})$  (Note that the  $\overline{CLK}$  and CLK have an overlap equal to an inverter delay  $(t_{I_0})$ )

Need to hold input (D), otherwise the master will latch new D value.

$$\bullet t_{pcq} = t_{T_3} + t_{I_6}$$

- $t_{hold} = t_{l_0} (t_{l_1} + t_{T_1} + t_{l_3})$  (Note that the  $\overline{CLK}$  and CLK have an overlap equal to an inverter delay  $(t_{l_0})$ )

- Need to hold input (D), otherwise the master will latch new D value.

$$\bullet t_{pcq} = t_{T_3} + t_{l_6}$$

$$t_{setup} = t_{I_1} + t_{T_1} + t_{I_3} + t_{I_4}$$

- $t_{hold} = t_{l_0} (t_{l_1} + t_{T_1} + t_{l_3})$  (Note that the  $\overline{CLK}$  and CLK have an overlap equal to an inverter delay  $(t_{l_0})$ )

- Need to hold input (D), otherwise the master will latch new D value.

$$\bullet t_{pcq} = t_{T_3} + t_{I_6}$$

$$t_{setup} = t_{I_1} + t_{T_1} + t_{I_3} + t_{I_4}$$

- $t_{hold} = t_{l_0} (t_{l_1} + t_{T_1} + t_{l_3})$  (Note that the  $\overline{CLK}$  and CLK have an overlap equal to an inverter delay  $(t_{l_0})$ )

- Need to hold input (D), otherwise the master will latch new D value.

$$\bullet t_{pcq} = t_{T_3} + t_{I_6}$$

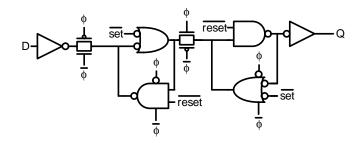

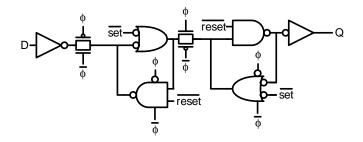

### ■ Set forces output high when enabled

Flip-flop with asynchronous set and reset

- Set forces output high when enabled

- Flip-flop with asynchronous set and reset

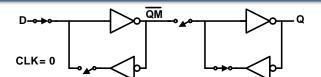

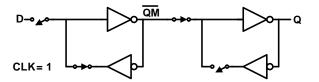

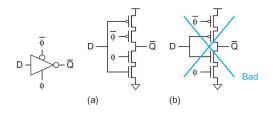

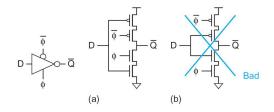

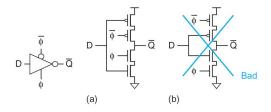

### A dynamic latch

sometimes called clocked CMOS (C<sup>2</sup>MOS) latch

second design is inferior as the input noise passed into the output when the latch is opaque

A dynamic latch

• sometimes called clocked CMOS ( $C^2MOS$ ) latch

second design is inferior as the input noise passed into the output when the latch is opaque

### A dynamic latch

- sometimes called clocked CMOS ( $C^2MOS$ ) latch

- second design is inferior as the input noise passed into the output when the latch is opaque

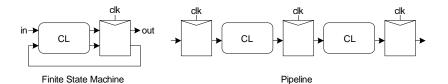

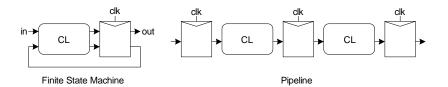

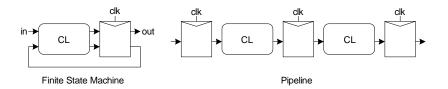

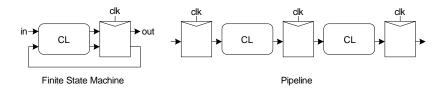

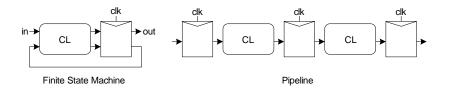

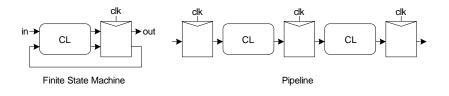

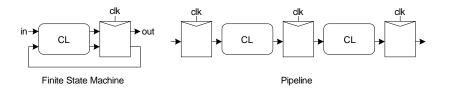

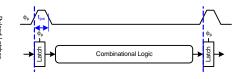

# Sequencing

### Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

# Sequencing

### Combinational logic

output depends on current inputs

## Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

### Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

- Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

- Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

- Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

- Combinational logic

- output depends on current inputs

- Sequential logic

- output depends on current and previous inputs

- Requires separating previous, current, future

- Called state or tokens

- Ex: FSM, pipeline

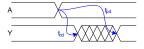

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

Delay fast tokens so they don't catch slow ones.

- If tokens moved through pipeline at constant speed, no sequencing elements would be necessary

- Ex: fiber-optic cable

- Light pulses (tokens) are sent down cable

- Next pulse sent before first reaches end of cable

- No need for hardware to separate pulses

- But dispersion sets min time between pulses

- This is called wave pipelining in circuits

- In most circuits, dispersion is high

- Delay fast tokens so they don't catch slow ones.

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence.

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

- Use flip-flops to delay fast tokens so they move through exactly one stage each cycle.

- Inevitably adds some delay to the slow tokens

- Makes circuit slower than just the logic delay

- Called sequencing overhead

- Some people call this clocking overhead

- But it applies to asynchronous circuits too

- Inevitable side effect of maintaining sequence

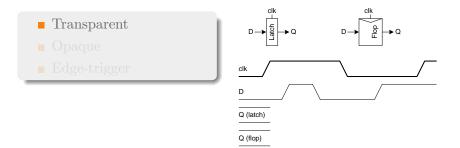

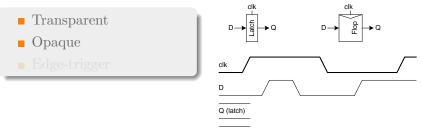

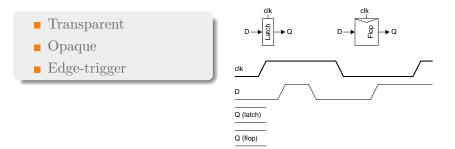

#### Latch: Level sensitive

- a.k.a. transparent latch, D latch

- Flip-flop: edge triggered

- a.k.a. master-slave flip-flop, D flip-flop, D register

#### Latch: Level sensitive

- a.k.a. transparent latch, D latch

- Flip-flop: edge triggered

- a.k.a. master-slave flip-flop, D flip-flop, D register

#### Latch: Level sensitive

• a.k.a. transparent latch, D latch

■ Flip-flop: edge triggered

a.k.a. master-slave flip-flop, D flip-flop, D register

#### Latch: Level sensitive

• a.k.a. transparent latch, D latch

■ Flip-flop: edge triggered

a.k.a. master-slave flip-flop, D flip-flop, D register

▲ □ ▶ ▲ 圖 ▶ ▲ 圖 ▶ ▲ 圖 ■ ● ● ● ●

Vishal Saxena | CMOS Inverter

Q (flop)

- Transparent

- Opaque

- Edge-trigger

- \* ロ \* \* 御 \* \* 国 \* \* 国 \* ・ 国 \* の & @

Vishal Saxena | CMOS Inverter

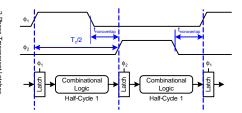

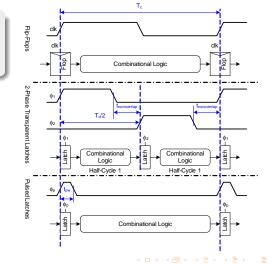

### Sequencing Methods

2-Phase Transparent Latches

- イロト イヨト イヨト イヨト ヨー わへぐ

- 2-phase latches

- Pulsed Latches

Pulsed Latches

### Sequencing Methods

Flip-flops2-phase latchesPulsed Latches

| Logic Prop. Delay             | A-                                                                                                                                                               |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Cont. Delay             |                                                                                                                                                                  |

| Latch/Flop Clk->Q Prop. Delay | 1                                                                                                                                                                |

| Latch/Flop Clk->Q Cont. Delay | 1                                                                                                                                                                |

| Latch D->Q Prop. Delay        | 1                                                                                                                                                                |

| Latch D->Q Cont. Delay        | 1                                                                                                                                                                |

| Latch/Flop Setup Time         | 1                                                                                                                                                                |

| Latch/Flop Hold Time          | 1                                                                                                                                                                |

|                               | Logic Cont. Delay<br>Latch/Flop Clk->Q Prop. Delay<br>Latch/Flop Clk->Q Cont. Delay<br>Latch D->Q Prop. Delay<br>Latch D->Q Cont. Delay<br>Latch/Flop Setup Time |

Table: Contamination and Propagation Delays

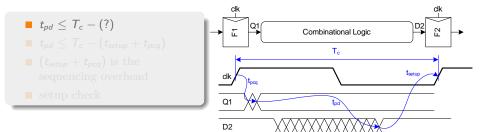

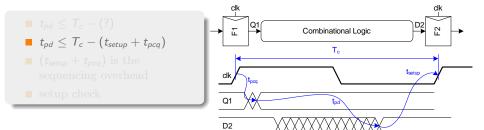

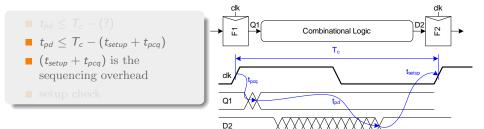

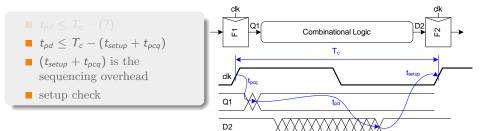

## Max-Delay:Flip-Flops

#### Vishal Saxena | CMOS Inverter

19/21

## Max-Delay:Flip-Flops

## Max-Delay:Flip-Flops

#### Vishal Saxena | CMOS Inverter

19/21

## Max-Delay:Flip-Flops

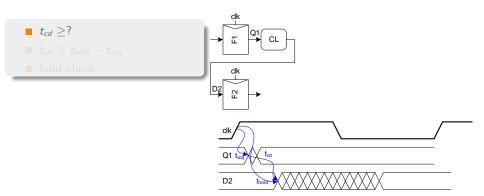

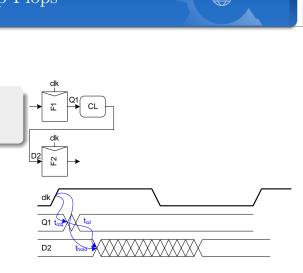

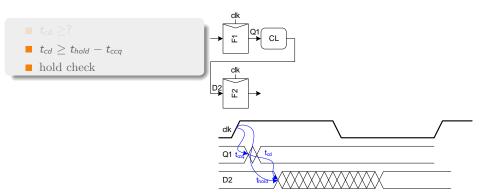

# Min-Delay:Flip-Flops

Vishal Saxena | CMOS Inverter

$t_{cd} \geq t_{hold} - t_{ccq}$

Vishal Saxena | CMOS Inverter

Vishal Saxena | CMOS Inverter

20/21

N. Weste and D. Harris, CMOS VLSI Design: A circuits and systems perspective, 4th Ed., Addison-Wesley, 2010.

R. J. Baker, CMOS Circuit Design, Layout and Simulation, revised 2nd Edition, Wiley-IEEE, 2008.

▲日 ▶ ▲ 聞 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q ()~