### CMOS Scaling

#### Vishal Saxena ECE, Boise State University

Oct 18, 2010

Vishal Saxena | CMOS Scaling

Moore's law today

Clock speeds have improved

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (L) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- **1**) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (L) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- 1) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (L) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- 1) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (*L*) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- 1) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (L) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- 1) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

- The increase in density of transistors is achieved by CMOS scaling

- the minimum channel length (L) is roughly scaled by a factor  $S = \frac{1}{\sqrt{2}}$  in every generation

- Two paradigms for device scaling:

- 1) Constant field scaling

- 2) Constant voltage scaling

- In practice a combination of both is used to scale CMOS devices

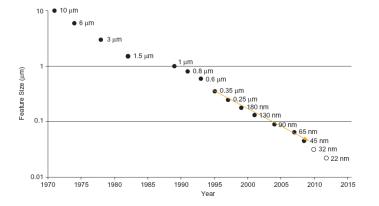

# CMOS Nodes with Scaling

Moore's Law CMOS Scaling

# Influence of Scaling on CMOS Devices

| Parameter                      | Sensitivity                    | Scaling Factor |

|--------------------------------|--------------------------------|----------------|

| Length: L                      |                                | S              |

| Width: $W$                     |                                | S              |

| GOX thickness: $t_{ox}$        |                                | S              |

| Supply Voltage: $V_{DD}$       |                                | S              |

| Threshold voltage: $V_{THN/P}$ |                                | S              |

| Substrate doping: $N_A$        |                                | 1/S            |

| β                              | $\frac{W}{L} \frac{1}{t_{ox}}$ | 1/S            |

| Current: Ion                   | $\beta (V_{DD} - V_{TH})^2$    | S              |

| Resistance: $R$                | $\frac{V_{DD}}{I_{on}}$        | 1              |

| Gate capacitance: $C_{ox}$     | $\frac{WL}{t_{ox}}$            | S              |

| Gate delay: $\tau$             | $R \cdot C_{ox}$               | S              |

| Clock frequency: $f_{clk}$     | $\frac{1}{\tau}$               | 1/S            |

#### Table: CMOS Scaling

Moore's Law CMOS Scaling

## Influence of Scaling on CMOS Devices contd.

| Parameter                      | Sensitivity        | Scaling Factor        |

|--------------------------------|--------------------|-----------------------|

| Dynamic power dissipation: $P$ | $CV^2 f_{clk}$     | <i>S</i> <sup>2</sup> |

| Chip area: A                   | $\sim$ WL          | <i>S</i> <sup>2</sup> |

| Power density                  | P/A                | 1                     |

| Current density                | I <sub>on</sub> /A | 1/S                   |

Table:CMOS Scaling contd.

Vishal Saxena | CMOS Scaling