# CREATING A PORTABLE PROGRAMMING ABSTRACTION FOR WAVEFRONT PATTERNS TARGETING HPC SYSTEMS

by

**Robert Searles**

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

Spring 2019

© 2019 Robert Searles All Rights Reserved

# CREATING A PORTABLE PROGRAMMING ABSTRACTION FOR WAVEFRONT PATTERNS TARGETING HPC SYSTEMS

by

**Robert Searles**

Approved: \_\_\_\_\_

Kathleen McCoy, Ph.D. Chair of the Department of Computer & Information Sciences

Approved: \_

Levi Thompson, Ph.D. Dean of the College of Engineering

\_\_\_\_\_

Approved: \_

Douglas J. Doren, Ph.D. Interim Vice Provost for Graduate and Professional Education I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

Sunita Chandrasekaran, Ph.D. Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Michela Taufer, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

Rui Zhang, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Wayne Joubert, Ph.D. Member of dissertation committee I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed:

Oscar Hernandez, Ph.D. Member of dissertation committee

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the support of my family, mentors, colleagues, and friends. First and foremost I would like to thank my parents, David and Rosanna Searles, for raising me in a wonderful, loving home and for giving me the best foundation possible. Their love and support set me up for success since the day I was born. I could not ask for better parents, mentors, and role models. I would like to thank my siblings, Paul and Victoria Searles, for being the best and most supportive siblings anyone could ask for. Both of you have been there for me since the day you were born. Without you, I would not be the man I am today. I would also like to thank my partner, Kayla Sampson, for all that she does for me, even when times are stressful. I am excited to start our life and our family together.

I am very fortunate to have had such amazing advisors during my time at UD. I would like to thank my undergraduate advisor, Dr. Terrence Harvey, for his years of support that have gone beyond the scope of my undergraduate education. I would also like to express my undying gratitude for both of my graduate advisors, Dr. John Cavazos and Dr. Sunita Chandrasekaran. As his undergraduate research assistant, Dr. Cavazos's mentorship encouraged me to pursue a graduate degree, and he offered to be my advisor in the process. Whether it meant staying up all night with me to meet paper deadlines, coming out to see me DJ at a local bar on the weekends, or wishing me well when I decided to pursue a different research direction, he was always there to support me. He is loved and missed. Dr. Chandrasekaran's mentorship is something I will never take for granted. She cares about each and every one of her students, and I am proud to be one of them. No matter how busy she gets, she always makes time to communicate with me and give me feedback on my work. She is an incredible role model to me, and I really appreciate all the time and energy she has invested toward my success. I would also like to thank my committee members, Dr. Rui Zhang, Dr. Michela Taufer, Dr. Wayne Joubert, and Dr. Oscar Hernandez for their guidance and mentorship. My research would not be possible without them.

Finally, I would like to thank my labmates, colleagues, and friends. I was fortunate to work with some amazing people throughout my time as a graduate student. I thank you all for your collaboration and support: Marco Alvarez, EJ Park, Sameer Kulkarni, William Killian, Tristan Vanderbruggen, Wei Wang, Lifan Xu, Amir Ashouri, Arnov Sinha, Kshitij Srivastava, Jose Monsalve Diaz, Sanhu Li, Eric Wright, Mauricio Ferrato, Dylan Chapp, and Michael Wyatt. I would also like to thank my friends and roommates. Whether you helped me put a roof over my head, shared laughs with me while playing video games to decompress, talked to me on the phone when I was stressed, or simply spent time with me on my nights off, know that you also played an integral role in my success: Matthew Senseny, Joseph DiGregorio, Mark Rushmere, Jacob Gaines, Stephen Herbein, Michael Bruno, Dylan Ross, Brandon Morris, Victoria Black, Logan Mears, Keith and Paige Parlier, Charlie Pens, Adam Petruzziello, Gerald Clericuzio, Michael Gallo, Aaron Yalcin, Arman Yalcin, Scott Ehrmann, James Murray, Adam Wisniewski, Emily Corbett, Jon Wentworth, David Blaha, Jesse Melvin, and Stephen Sprofera. Thank you all from the bottom of my heart.

This material is based upon work supported by the National Science Foundation (NSF) under grant no. 1814609.

This material is based upon work supported by the U.S. Department of Energy, Office of science, and this research used resources of the Oak Ridge Leadership Computing Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-00OR22725.

I would also like to thank NVIDIA Corporation for donating the TITAN Xp, TITAN V, Tesla P40, and Tesla V100 GPUs used to prototype code for this research and for providing access to their Professional Service Group (PSG) machine that I used for this work.

### TABLE OF CONTENTS

| LIST OF TABLESxiLIST OF FIGURESxiiABSTRACTxiv |                     |                                                                            |                  |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|--|--|--|

| Chapter                                       |                     |                                                                            |                  |  |  |  |  |  |  |  |  |  |  |

| 1                                             | MO                  | MOTIVATION AND PROBLEM STATEMENT                                           |                  |  |  |  |  |  |  |  |  |  |  |

|                                               | $1.1 \\ 1.2 \\ 1.3$ | Thesis Objective                                                           | 1<br>1<br>1      |  |  |  |  |  |  |  |  |  |  |

| <b>2</b>                                      | INT                 | TRODUCTION                                                                 | 3                |  |  |  |  |  |  |  |  |  |  |

|                                               | $2.1 \\ 2.2$        | On-Node High-Level Programming Models                                      | $\frac{3}{4}$    |  |  |  |  |  |  |  |  |  |  |

|                                               |                     | 2.2.1       Parallelism                                                    | 5<br>5<br>5<br>6 |  |  |  |  |  |  |  |  |  |  |

|                                               | 2.3                 | Directive Based Programming Model: OpenACC                                 | 6                |  |  |  |  |  |  |  |  |  |  |

|                                               |                     | 2.3.1OpenACC Execution Model                                               | 7<br>8           |  |  |  |  |  |  |  |  |  |  |

|                                               | 2.4                 | Complex Parallel Pattern: Wavefront                                        | 9                |  |  |  |  |  |  |  |  |  |  |

| 3                                             | LIT                 | ERATURE REVIEW/RELATED WORK                                                | 12               |  |  |  |  |  |  |  |  |  |  |

|                                               | 3.1                 | Performance Optimization and Auto-Tuning of Code Targeting<br>Accelerators | 12               |  |  |  |  |  |  |  |  |  |  |

|   | 3.2                                                                            | Malware Detection Strategies                                                                                                                                                                                                                       | 13                                     |  |  |  |  |  |  |  |

|---|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

|   |                                                                                | <ul><li>3.2.1 Graph-Based Malware Detection</li></ul>                                                                                                                                                                                              | $\begin{array}{c} 13\\15\end{array}$   |  |  |  |  |  |  |  |

|   | $3.3 \\ 3.4$                                                                   | Leveraging Heterogeneous HPC Hardware for Big Data Applications .<br>Wavefront Algorithm Parallelization                                                                                                                                           | $\begin{array}{c} 15\\ 16 \end{array}$ |  |  |  |  |  |  |  |

| 4 | MO                                                                             | TIVATION FOR USING ACCELERATORS                                                                                                                                                                                                                    | 19                                     |  |  |  |  |  |  |  |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                      | Auto-Tuning GPU Accelerated Applications Using High-LevelLanguagesLanguagesParallelization of Graph-Based Machine Learning for Malware DetectionA Portable, High-Level Graph Analytics Paradigm TargetingDistributed, Heterogeneous SystemsSummary | 19<br>20<br>23<br>25                   |  |  |  |  |  |  |  |

| 5 |                                                                                | EXPLORING A COMPLEX PARALLEL PATTERN:<br>WAVEFRONT                                                                                                                                                                                                 |                                        |  |  |  |  |  |  |  |

| 6 | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                     | Wavefront Parallel Patterns                                                                                                                                                                                                                        | 26<br>27<br>29<br>30                   |  |  |  |  |  |  |  |

| 0 | DESIGNING SOFTWARE ABSTRACTIONS IN<br>PROGRAMMING MODELS FOR WAVEFRONT PATTERN |                                                                                                                                                                                                                                                    |                                        |  |  |  |  |  |  |  |

|   | $6.1 \\ 6.2 \\ 6.3$                                                            | Analyzing the Flow of Data and Computation in a Wavefront Model<br>The Memory Model Abstraction                                                                                                                                                    | 31<br>33<br>34                         |  |  |  |  |  |  |  |

|   |                                                                                | <ul> <li>6.3.1 What is the Koch-Baker-Alcouffe (KBA) Method?</li> <li>6.3.2 High-Level Extension for Wavefront Codes</li> <li>6.3.3 Exploring Asynchronous Execution to Saturate Massively Parallel Processors</li></ul>                           | 35<br>38<br>38<br>39                   |  |  |  |  |  |  |  |

### 7 WAVEBENCH: A TOOL TO MODEL THE PERFORMANCE

|              | IM                | PACT OF WAVEFRONT PARALLELISM                                                            | 43                     |

|--------------|-------------------|------------------------------------------------------------------------------------------|------------------------|

|              | 7.1               | Introducing Wavebench                                                                    | 43                     |

|              |                   | 7.1.1Local Sequence Alignment                                                            | $43 \\ 45 \\ 45 \\ 45$ |

|              | $7.2 \\ 7.3$      | Evaluation & ResultsPath Forward                                                         | 48<br>53               |

| 8            | RE                | AL-WORLD CASE STUDY: MINISWEEP                                                           | 54                     |

|              | 8.1               | Overview of Sweep Algorithm                                                              | 56                     |

|              |                   | 8.1.1Grid-level computations8.1.2Gridcell-level computations8.1.3Summary of problem axes | 56<br>56<br>57         |

|              | 8.2<br>8.3<br>8.4 | Parallelizing the Sweep Algorithm                                                        | 58<br>60<br>63         |

|              |                   | 8.4.1       CUDA                                                                         | 63<br>65<br>65<br>68   |

|              | 8.5               | Programming Model Limitations                                                            | 69                     |

|              |                   | 8.5.1       General                                                                      | 70<br>71<br>72<br>72   |

|              | $8.6 \\ 8.7$      | Profiling Minisweep                                                                      | 74<br>76               |

| 9            | CO                | NCLUSION & FUTURE WORK                                                                   | 82                     |

| B            | IBLI              | OGRAPHY                                                                                  | 85                     |

| $\mathbf{A}$ | ppen              | lix                                                                                      |                        |

| RELATED RESC | OURCES | 5 |  |   |  |  |  |   |  |  |  |  |  |  | 97        |

|--------------|--------|---|--|---|--|--|--|---|--|--|--|--|--|--|-----------|

| PERMISSIONS  |        |   |  | • |  |  |  | • |  |  |  |  |  |  | <b>98</b> |

### LIST OF TABLES

| 4.1 | Comparing similarity matrix computation time for each dataset.<br>Runtimes (h: hours, m: minutes, s: seconds) are presented for each<br>implementation. Below each runtime we give speedup compared to<br>the best OpenMP (OpenMP Matrix) implementation is shown.<br>VRAM limitation was exceeded for our larger datasets when only<br>running on the GPU. | 22 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | Specifications of the nodes in the systems we used to test different                                                                                                                                                                                                                                                                                        |    |

|     | configurations of Wavebench.                                                                                                                                                                                                                                                                                                                                | 48 |

| 7.2 | Problem sizes used to test Wavebench's Gauss-Seidel algorithm                                                                                                                                                                                                                                                                                               | 49 |

| 7.3 | Problem sizes used to test Wavebench's radiation transport algorithm.                                                                                                                                                                                                                                                                                       | 50 |

| 8.1 | Problem dimensions mapping to thread hierarchy                                                                                                                                                                                                                                                                                                              | 63 |

| 8.2 | Specifications of the nodes in the systems we used to test different configurations of Minisweep                                                                                                                                                                                                                                                            | 76 |

| 8.3 | Comparative performance on several platforms                                                                                                                                                                                                                                                                                                                | 77 |

### LIST OF FIGURES

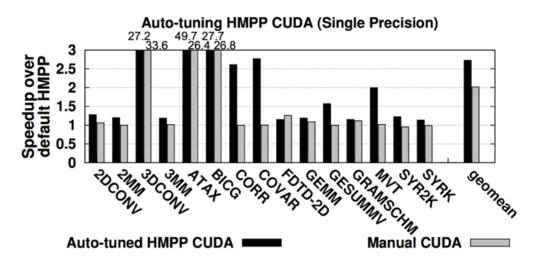

| 4.1 | Single precision speedup graph comparing the performance of auto-tuned HMPP code against manually written CUDA code                                                                                                                                                                                 | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

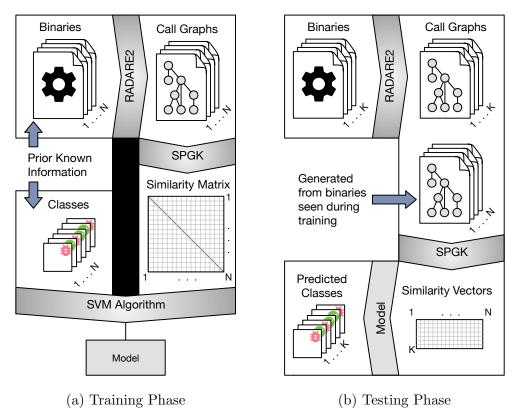

| 4.2 | Figure 4.2a shows the workflow toward construction of a machine learning model generated during this work's training phase.<br>Figure 4.2b shows a flow diagram demonstrating the classification of an unseen binary application used during the evaluation phase                                   | 21 |

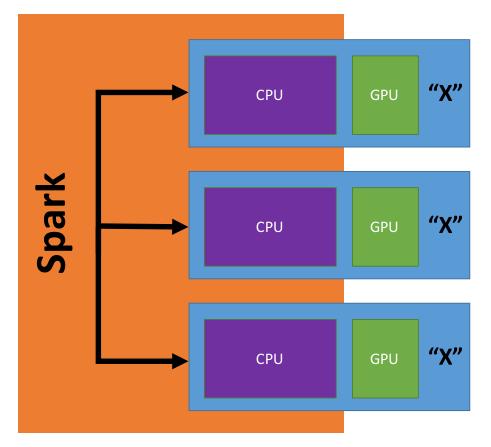

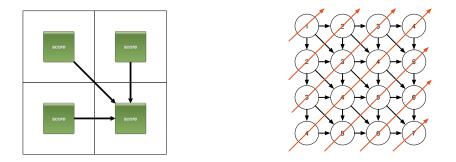

| 4.3 | A high-level depiction of the proposed paradigm, which uses Spark for data/task distribution in conjunction with a local computational framework (X) on each node.                                                                                                                                  | 24 |

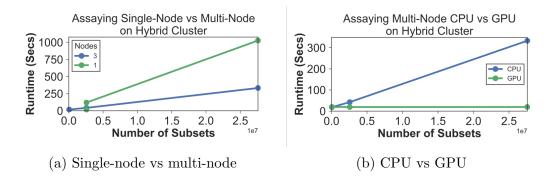

| 4.4 | Runtime results for Graph Assaying run on the hybrid cluster $\ . \ .$                                                                                                                                                                                                                              | 25 |

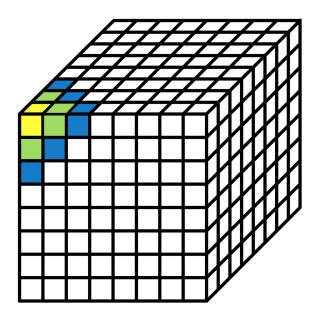

| 5.1 | Minisweep's wavefront computational pattern                                                                                                                                                                                                                                                         | 27 |

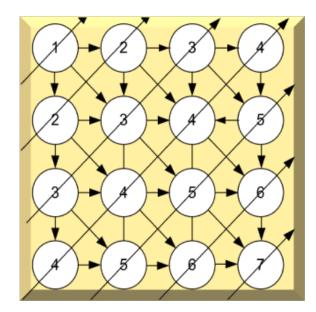

| 5.2 | Smith Waterman's wavefront computational pattern                                                                                                                                                                                                                                                    | 28 |

| 6.1 | An example of our extension to the OpenACC standard. Note that<br>the dimensionality of the wavefront component is specified in the<br>directive so that the preprocessor knows how many loops within the<br>loop nest to consider when performing the requested transformation<br>of the loop nest | 40 |

| 7.1 | Local Sequence Alignment gridcell dependency and in-gridcell computation                                                                                                                                                                                                                            | 44 |

| 7.2 | 2D wavefront dependency exhibited by the Local Sequence Alignment algorithm                                                                                                                                                                                                                         | 44 |

| 7.3 | Local Sequence Alignment loop nest                                                                                                                                                                                                                                                                  | 44 |

| 7.4 | Gauss-Seidel gridcell dependency and in-gridcell computation $\ldots$                                                                                                                                                                                                                               | 45 |

| 7.5 | Gauss-Seidel loop nest                                                                                                                                                                                                                                                                              | 45 |

| 7.6  | Radiation Transport gridcell dependency and in-gridcell computation                                                                                                                                                                                                                                                                                              | 46  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.7  | 3D wavefront dependency exhibited by the Radiation Transport algorithm                                                                                                                                                                                                                                                                                           | 46  |

| 7.8  | Radiation Transport loop nest                                                                                                                                                                                                                                                                                                                                    | 47  |

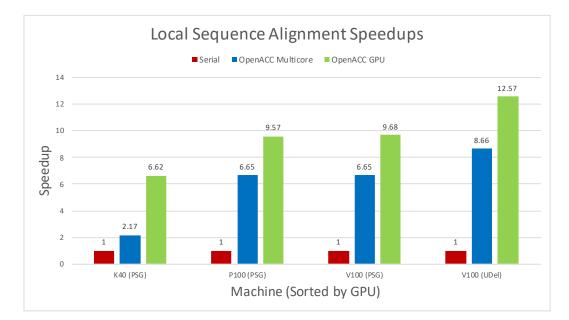

| 7.9  | Local Sequence Alignment speedups                                                                                                                                                                                                                                                                                                                                | 49  |

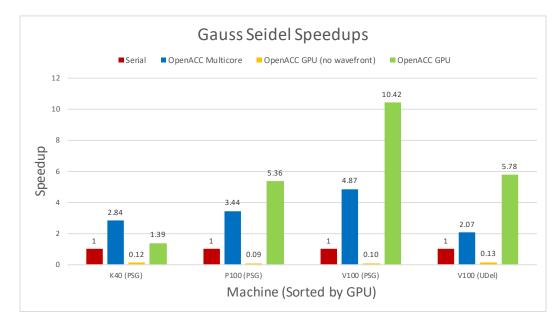

| 7.10 | Gauss-Seidel speedups                                                                                                                                                                                                                                                                                                                                            | 51  |

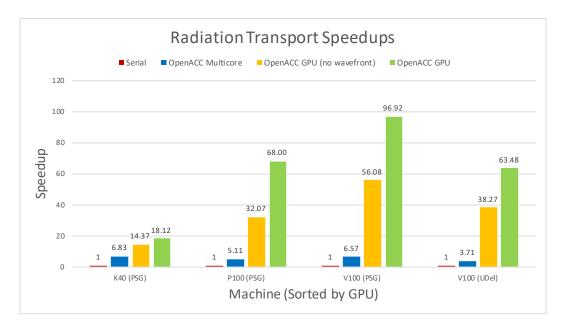

| 7.11 | Radiation Transport speedups                                                                                                                                                                                                                                                                                                                                     | 53  |

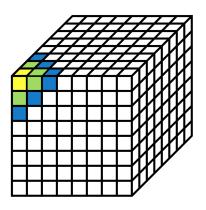

| 8.1  | KBA parallel wavefront algorithm                                                                                                                                                                                                                                                                                                                                 | 59  |

| 8.2  | Abstract representation of sweep algorithm                                                                                                                                                                                                                                                                                                                       | 64  |

| 8.3  | Sweep loop nest with OpenACC annotations                                                                                                                                                                                                                                                                                                                         | 66  |

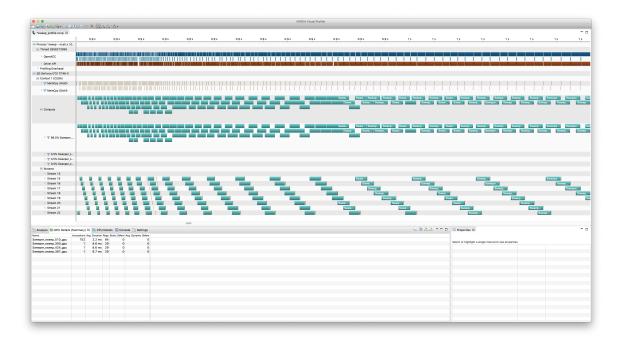

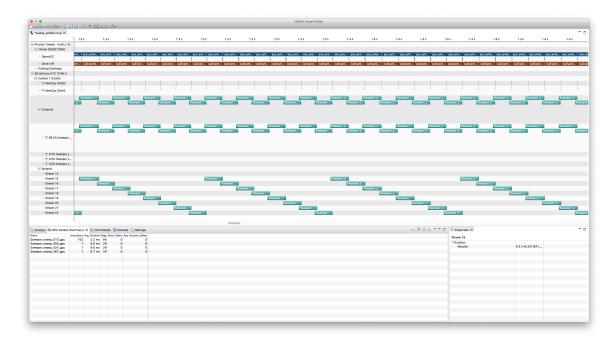

| 8.4  | Examining Minisweep's execution using <i>pgprof</i> . The beginning of execution is shown here.                                                                                                                                                                                                                                                                  | 75  |

| 8.5  | Examining Minisweep's execution using $pgprof$ . The most compute intensive portion of execution is shown here                                                                                                                                                                                                                                                   | 75  |

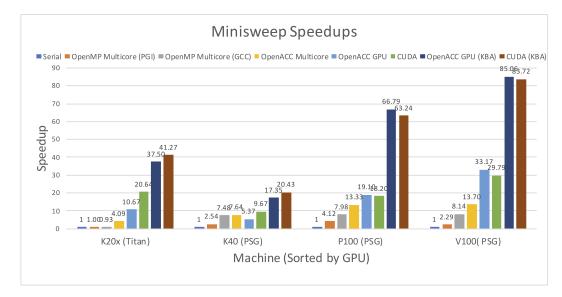

| 8.6  | Minisweep's speedups over serial using different runtime<br>configurations sorted according to each machine's GPU. Note that<br>the CUDA version is parallelized along the same dimensions as the<br>OpenACC GPU configuration. The corresponding KBA<br>configurations utilize the KBA blocking method for additional<br>parallelism across spatial dimensions. | 78  |

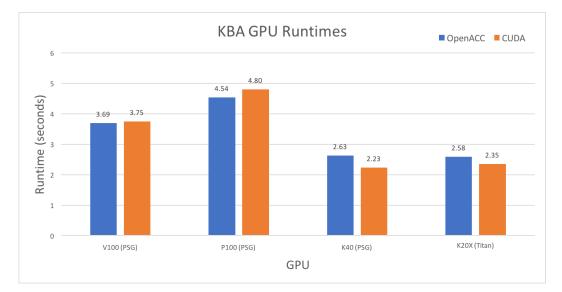

| 8.7  | Absolute runtimes (measured in seconds) of OpenACC and CUDA experiments on all GPUs used. Note that the V100/P100 problem size is an order of magnitude larger than the K40/K20x configuration, as mentioned earlier.                                                                                                                                            | 79  |

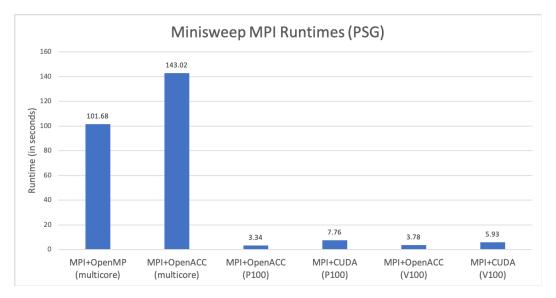

| 8.8  | Minisweep's runtimes when running on 4 nodes (each with 4 GPUs) using 16 MPI ranks (1 rank per GPU). Lower is better. Note that the runtimes of OpenACC and CUDA are comparable even when run on multiple nodes. This reinforces our conclusions drawn from                                                                                                      | 0.0 |

|      | Figure 8.6                                                                                                                                                                                                                                                                                                                                                       | 80  |

#### ABSTRACT

Processor architectures have been rapidly evolving for decades. From the introduction of the first multicore processor by IBM in 2001 [2] to the massively parallel supercomputers of today, the exploitation of parallelism has become increasingly important, as the clock rates of a single core have plateaued. Heterogeneity is also on the rise since the revelation that domain-specific pieces of hardware (GPUs) could be repurposed for generalized parallel computation [10]. This shift has prompted the need to rethink algorithms, languages, and programming models in order to increase parallelism from a programming standpoint and migrate large scale applications to today's massively powerful platforms. This is not a trivial task, as these architectures and systems are still undergoing constant evolution. More recently, supercomputing centers are transitioning toward utilizing fat-nodes (nodes with even more cores due to the presence of multiple accelerators) in order to reduce node count and the overhead associated with cross-node communication. For example, Oak Ridge National Laboratory's TITAN supercomputer (OLCF-3), which was built in 2011, was comprised of 18,688 nodes, each containing a single NVIDIA Tesla K20x GPU accelerator [60]. In 2018, less than a decade later, ORNL constructed the Summit supercomputer (OLCF-4), consisting of 4,608 nodes, each equipped with six NVIDIA Tesla V100 GPU accelerators [67].

The trend toward fat-node based systems illustrates the importance of on-node programming models. Low-level languages like CUDA and OpenCL offer direct control over GPU hardware, but they incur a learning curve and lack portability, which are concerns for application developers. It is a huge time sink to have to learn a hardware-specific low-level language, port your code using that language, and then reimplement that same code when a newer GPU (or non-GPU) architecture emerges. The demand for portable solutions for programming parallel systems with minimal programmer overhead lead to the creation of directive-based programming. Directive-based programming models, such as OpenMP [106] and OpenACC [40, 24, 105], allow programmers to simply annotate their existing code with statements that describe the parallelism found within that code. A compiler then translates this into code that can run on a specified target architecture. This type of programming approach has become increasingly popular amongst industry scientists [9]. Although directive-based programming models allow programmers to worry less about programming and more about science, expressing complex parallel patterns in these models can be a daunting task, especially when the goal is to achieve the theoretical maximum performance that today's hardware platforms are ready to offer. One such parallel pattern commonly found in scientific applications is called wavefront.

This thesis examines existing state-of-the-art wavefront applications and parallelization strategies, which it uses to create a high-level abstraction of wavefront parallelism and a programming language extension that facilitates an easy adaptation of such applications in order to expose parallelism on existing and future HPC systems. This thesis presents an open-source tool called Wavebench, which uses wavefront algorithms commonly found in real-world scientific applications to model the performance impact of wavefront parallelism on HPC systems. This thesis also uses the insights gained during the creation of this tool to apply the developed, high-level abstraction to a real-world case study application called Minisweep: a mini-application representative of the main computational kernel in Oak Ridge National Laboratory's Denovo radiation transport code used for nuclear reactor modeling. The OpenACC implementation of this abstraction running on NVIDIA's Volta GPU (present in ORNL's *Summit* supercomputer) boasts an 85.06x speedup over serial code, which is larger than CUDAs 83.72x speedup over the same serial implementation. This serves as a proof of concept for the viability of the solutions presented by this thesis.

#### Chapter 1

#### MOTIVATION AND PROBLEM STATEMENT

#### 1.1 Thesis Objective

The objective of this thesis is to explore and develop a high-level programming abstraction for a complex parallel pattern called wavefront that is commonly found in real-world scientific applications.

#### 1.2 Contributions

- 1. Design and create a standardized high-level programming abstraction (language extension) to be effectively mapped onto heterogeneous parallel architectures for the wavefront parallel pattern

- 2. Evaluate this abstraction on multiple state-of-the-art platforms using a tool we created to model the performance impact of the developed abstraction

- 3. Apply this abstraction to a real-world scientific application of broad interest

#### 1.3 Organization

This thesis is organized as follows. Chapter 2 will provide background information on the state-of-the-art high-level programming models, motivate the need for extensions, and introduce the wavefront parallel pattern we will examine in order to meet our goals. Chapter 3 will outline the related work in regards to the wavefront pattern in the scope of high performance computing. Chapter 4 will outline the author's HPC background and past work that led up to this thesis. Chapter 5 will define the wavefront parallel pattern, as well as outline the goals of this thesis in regards to extending existing programming models in order to support this pattern. Chapter 6 will lay out the strategy the author used to accomplish these goals, and it will also present a preprocessor that applies appropriate code transformations, which serves as a proof of concept for the discussed strategy. Chapter 7 presents a tool the author developed to help model the performance impact of wavefront parallelism using wavefront algorithms found in many real-world scientific applications. Chapter 8 shows the author's methodology at work as the developed abstraction is applied to a real-world scientific application that is in use today as part of an Exascale project and presents associated results. Finally, this thesis concludes in Chapter 9.

## Chapter 2 INTRODUCTION

Hardware architectures are rapidly evolving. High performance computing nodes are becoming increasingly heterogeneous, including the current and anticipated exascale accelerated node architectures [14], which are expected to contain a mix of throughput and latency optimized cores [102]. Since throughput cores will be more numerous on these machines, an application can achieve high performance if its algorithm exhibits a greater degree of parallelism, thus keeping all the cores on the chip busy. Latency optimized cores, lesser in count, will prioritize serial performance and deal with expensive memory accesses. Such a balanced mixture of cores is expected to manage different types of parallelism available in an algorithm. Memory has advanced as well. 3D memory stacking with memory moving onto the socket provide increased bandwidth and faster communication.

#### 2.1 On-Node High-Level Programming Models

Such diverse architectures require their own code optimization strategies. Application developers prefer a "write-once" code development strategy in which a single piece of code will execute efficiently and portably on all targeted architectures. However, it is required that a programming model not be designed with just the underlying hardware in mind. Its implementation is also expected to address requirements of applications and its algorithms. The programming language that implements the model should provide the right abstractions to improve the productivity of scientific developers. Programmers often resort to a trade-off between achieving portability and high performance. Why? The issue is two-fold. Adequate application parallelism will not be exposed on a particular hardware architecture if the algorithm is structured in a way that limits the level of concurrency that a programming model can exploit. Secondly, a performance-portable single code representation is only possible if the programming abstractions are carefully crafted in a way that allows the programming models to provide informative hints to the compilers in order to generate optimized code across platforms.

Some of the most widely used types of on-node programming models that provide developers with such abstractions are based on directives: annotations added to existing serial code used to instruct the compiler as to how the code is meant to run on parallel architectures. Directives allow us to abstract the rich feature set of hardware architectures, incrementally improve, port, and maintain the codebase across platforms. Two of the most widely used directive-based programming models are OpenMP and OpenACC. OpenMP is a multi-platform, shared memory multiprocessing API that has been around since 1997 [34]. In 2015, it started supporting offloading features, such as the ability to target multiple devices within a system [106]. OpenMP 4.5 is being deployed to applications, e.g., Pseudo-Spectral Direct Numerical Simulation-Combined Compact Difference (PSDNS-CCD3D) [32], a computational fluid dynamics code on turbulent flow simulation using GPUs on the ORNL Titan system. OpenACC started in 2012 as a directive-based model for general purpose GPU (GPGPU) programming, and it has since been generalized to support many kinds of heterogeneous systems, including multi-core CPUs, GPUs, and FPGAs [40, 24]. Since its inception, it has been widely used to port large-scale applications spanning several domains such as AN-SYS [95], GAUSSIAN [43], and Icosahedral non-hydrostatic (ICON) [96] to massively parallel architectures.

#### 2.2 Essential Features of High-Level Programming Models

Directive-based models, along with other types of high-level programming models, aim to provide developers with four key features: parallelism, performance, programmability, and portability.

#### 2.2.1 Parallelism

The stagnation of processor clock rates due to power consumption and cooling challenges has ended the era of sequential computing. Instead, industry has shifted its focus to parallel architectures as a way to increase on-chip performance. At the node level, multi-core processors have become ubiquitous. In addition, enterprise-grade systems utilize multiple nodes connected via some type of network in order to provide an additional layer of parallelism and computational power. These "supercomputers" are representative of the way in which hardware trends are evolving. As a result, parallelism is the foundation of any modern programming model.

#### 2.2.2 Performance

There are many different types of parallel architectures, such as multi-core CPUs, Graphics Processing Units (GPUs), and Field-Programmable Gate Arrays (FP-GAs), all of which benefit from different types of optimizations. A high-level programming model should aim to provide a way for developers to tune their applications to be performant on the architecture they intend to run their application on. Ideally, this type of architecture-specific optimization can be handled automatically by the compiler, requiring only that the programmer specify the target architecture at compile time. This ensures that the code will perform as optimally as manually written, low-level code specific to that architecture [46].

#### 2.2.3 Programmability

As mentioned in Section 2.2.2, there are many different types of parallel architectures. In addition, heterogeneous hardware (hardware that combines elements of multiple architectures) is becoming increasingly common. Multi-node systems add an additional layer of complexity to the equation. Programming one node is hard. Programming many nodes is harder. Programming models must provide developers with a concise way of representing how their code should run on a parallel system, so that they only need to write their application once. That code should be generalized enough that it can be compiled into machine code that will run on any supported parallel architecture, including heterogeneous ones. These models should also provide a method for distributing computational tasks within an application across multiple nodes, as multi-node systems are becoming more and more common.

#### 2.2.4 Portability

Finally, a programming model should aim to be portable. It is not enough to simply represent code in a way that is conducive to compilation on existing architectures. Architectures are constantly evolving, and we cannot predict what future systems will look like. For example, ORNL's Titan supercomputer is a GPU-based, multi-node machine that presented a number of programming challenges when it was first built [60]. ORNL's newest machine, Summit [67], adds another layer of complexity in that each node will be equipped with 6 NVIDIA Volta GPUs, unlike Titan, which only contained one GPU per node. High-level programming models must be robust enough to handle these types of evolutionary challenges. An inability to due so motivates the need for changes and/or extensions in order to keep up with future hardware trends.

#### 2.3 Directive Based Programming Model: OpenACC

The on-node programming model this thesis aims to extend is OpenACC. OpenACC is a performance-portable, directive-based parallel programming model that targets modern heterogeneous HPC hardware [105]. The compiler directives that it provides can be used to annotate loops and regions of code that exhibit parallelism. The programmer can also specify a target at compile time to let the compiler know what type of hardware is being targeted based on the annotated code regions. Supported hardware includes multicore CPUs, as well as various types of accelerators, including Intel's Xeon Phi and many generations of NVIDIA's GPUs.

Another advantage of OpenACC is that when targeting accelerators, programmers do not have to explicitly manage data movement between the host (CPU) and accelerator(s), nor do they have to manually initiate the startup and shutdown of the accelerator(s). Instead, this is handled by the OpenACC compiler and runtime environment. These features dramatically reduce the amount of programmer overhead that is necessary, preserve performance, and allow for the creation of a single, portable codebase that will run on many different types of HPC hardware and systems. This section will present key features of OpenACC's execution and memory models that are used throughout this thesis.

#### 2.3.1 OpenACC Execution Model

OpenACC employs a host-directed execution model. What this means is that most of a programmer's application executes within a host thread, and compute intensive parallel regions (denoted by directive annotations) are offloaded either to multiple host cores (multicore CPU) or an accelerator (such as a GPU). The OpenACC specification refers to the host thread as the *host* and the parallel hardware, whether it be a multicore CPU or an accelerator, as the *device*. The job of the device is to execute portions of the code that are annotated with directives. These portions can be *parallel regions*, which are regions of code that contain parallel loops specified by the programmer, *kernels regions*, which contain loops to be executed as kernels that are determined by the compiler to be parallelizable, or *serial regions*, which contain blocks of sequential code.

Since many parallel regions contain multi-dimensional loop nests and modern accelerators and multicore CPUs support multiple levels of parallelism, OpenACC provides clauses the programmer can use within a directive to describe which portions of a loop nest should execute at what level. Accelerators and multicore CPUs both support coarse-grained parallelism: fully parallel execution across execution units with limited synchronization support. OpenACC exposes coarse-grained parallelism via the gang clause. Most accelerators and some multicore CPUs also support fine-grained parallelism: multiple execution threads within a single execution unit. OpenACC exposes fine-grained parallelism via the worker clause. Last, most accelerators and multicore CPUs support SIMD operations within execution units. OpenACC exposes these operations via the *vector* clause. It is the job of the programmer to understand the difference between these levels of parallelism and know which portions of their code can execute in what manner in order to properly annotate their source code for parallel execution.

Another useful feature of OpenACC is its *async* clause, which can be used to allow the host and device to execute portions of code asynchronously. This is useful in a couple of ways. First, it can be used to allow multiple parallel regions to execute asynchronously on a device (or across multiple devices). This is appropriate when a single parallel compute region is unable to utilize all available computational power a device has to offer or when there is so much work in a single compute region that the programmer decides it would be advantageous to split it up and run portions of that region on different devices, yielding additional parallelism. Second, it can be useful in overcoming some of the overhead associated with data movement between the host and device. By allowing the host thread to continue execution while a parallel region is offloaded to the device, the host thread can begin to transfer data to the device that will be needed for a compute region yet to run, rather than waiting for an unrelated compute region to complete execution before beginning the data transfer.

#### 2.3.2 OpenACC Memory Model

One defining characteristic of a host/device execution model is that device memory may be separate from host memory. For example, GPUs have their own onboard memory, which is separate from the rest of the system's memory. In such a system, the host thread is unable to read or write device memory, since it is not part of the host thread's virtual memory space, and the device is similarly unable to read or write host memory in most cases. Certain devices do provide the ability to read and write host memory, but such operations typically incur a significant performance penalty. Instead, all data movement between host and device memory must be performed by the host thread through explicit system calls. Fortunately, OpenACC provides directives for managing data movement between the host and device. The compiler takes care of generating the appropriate system calls, but the programmer needs to be aware of what is actually happening on the back end. Typically, data transfer overhead is where most parallel applications that utilize an accelerator suffer performance losses. If data movement is not efficiently managed, these losses can even be so big as to outweigh the computational benefit of using the accelerator, resulting in a slowdown of overall application performance. Device memory also tends to be much smaller than host memory, so there is a limit to how much data can be offloaded onto an accelerator, which in turn prohibits the amount of associated computation that can be offloaded via a single data transfer.

Some types of accelerators (such as GPUs) employ what is known as a weak memory model: they do not support memory coherence across different threads. This can create issues where results cannot be guaranteed for each execution of the same program. For example, if two threads within a parallel compute region write to the same location in memory, results may differ. Compilers usually can detect such cases, but it is still possible to write a compute region where this behavior exists, and thus, produces inaccurate results. Similarly, programmers need to be aware of whether data synchronization between the host and device is necessary. If a compute region offloads data to the device and that same data is read by the host during execution later on, it is important to ensure that the data has been synchronized back on the host-side before the host thread reaches that point in execution. This can become a problem when haphazardly utilizing OpenACC's *async* compute clause. OpenACC provides a number of clauses for use with its *data* directive in order to manage data transfer and synchronization between the host and device.

#### 2.4 Complex Parallel Pattern: Wavefront

Despite the widespread impact that existing high-level programming models have had on HPC in recent years, there still remains a gap in the way that they do not adequately expose and parallelize some of the complex algorithms often found in scientific applications. One such case is a wavefront-based algorithm that is of critical importance to solving scientific problems in multiple science domains. They are useful for problems for which the result values that are computed have dependencies, requiring that results be computed in stages (wavefronts), for which each stage's results depends on results computed in previous stages. The result is a limited amount of parallelism; all the elements of each stage can be computed in parallel as long as their dependencies from the previous stage are satisfied. Some examples of applications that can expose and exploit this type of wavefront parallelism include linear systems solvers, such as the Gauss-Seidel method [61], genome sequencing algorithms, such as Smith-Waterman [104], characterisation of chromosomal rearrangement, such as the Juicer/HiC tool [38, 51], and radiation transport codes [100, 66, 8].

This thesis aims to develop a viable extension to a directive-based programming model, by creating a high-level representation of the wavefront parallel pattern. Although our developed extension uses OpenACC, it can be considered for OpenMP as well without needing to change its functionality. Currently, such an abstraction does not exist, despite the prevalence of wavefront parallelism found in real-world applications. We support our abstraction with a tool we developed, called Wavebench, that is used to model the performance of different types of wavefront applications on hardware architectures found in state-of-the-art HPC systems. Our Wavebench tool features a collection of wavefront algorithms that are representative of the different types of computation found in the aforementioned applications. Throughout, we maintain a single codebase that can be used to target different types of existing HPC systems, ranging from multicore CPU-based systems, to heterogeneous GPU-based systems.

We also present a real-world case study application that is illustrative of the complexities in a wavefront-based algorithm: the Minisweep proxy application [78]. Parallelizing this application using current directive-based APIs will help reveal the gaps in their expressivity and features. We address this issue by designing and envisioning an abstract parallelism model that represents these gaps with a combination of notations. Integrating these notations into a programming language are key to exposing and mapping wavefront-based parallelism across HPC hardware architectures.

#### Chapter 3

#### LITERATURE REVIEW/RELATED WORK

This chapter presents work related to the prior research leading up to this thesis, as well as work that helps motivate the goals of this thesis. The discussed topics include auto-tuning code targeting accelerators, accelerating malware detection algorithms, and leveraging heterogeneous hardware in order to solve Big Data problems.

## 3.1 Performance Optimization and Auto-Tuning of Code Targeting Accelerators

Performance-portable code generation has been a popular field of research for decades. There are a number of library generators that automatically produce high-performance kernels, including FFT [41, 88, 119], BLAS [115, 123, 27, 44, 49], Sparse Numerical Computation [56, 112, 77, 22, 73], and domain specific routines [21, 31, 48]. Other research expands automatic code generation to routines whose performance depends not only on architectural features, but also on input characteristics [74, 75, 50]. These systems are a step toward automatically generating performance-portable code for different architectures. However, these prior works have been largely focused on small domain-specific kernels.

There is also related work on GPU code optimization that looked at a number of manual optimizations of CUDA kernels, including tiling, pre-fetching, and full loop unrolling within CUDA kernels [93]. Some researchers looked at varying thread block dimensions [76]. Others studied loop unrolling extensively as optimizations in CUDA kernels, but they were concerned with improving the performance of a single application [20]. A domain-specific auto-tuning framework for sparse matrix-vector multiplication on the GPU exists [30], and 3D-FFT of varying transform sizes on GPUs has been optimized using auto-tuning [82]. These two related works applied auto-tuning to specific applications, but not in a general sense. Another related work is the CUDA-CHiLL project, which can translate loop nests to high performance CUDA code [92]. The developers of this project provide a programming language interface that uses an embedded scripting language to express transformations or recipes. While this work supports CUDA transformations, it relies on the creation of an external script, which is not as convenient as using a directive-based approach like OpenMP or OpenACC.

The work presented here provides additional motivation behind the notion that code transformations can provide huge performance benefits to applications. However, these code transformations prove inconvient to implement most of the time. In order for high-level programming models to grow in popularity, they have to begin to tackle some of this more complex behavior without creating considerable additional programmer overhead.

#### **3.2** Malware Detection Strategies

In this section, we examine previous works on malware detection strategies that make use of various compiler representations and techniques (particularly graphs), and graph kernel parallelization. The work presented here proves that while these strategies are viable, they are very computationally intensive. Utilizing accelerators can help overcome the computational overhead created by these strategies, but programming these accelerators proves to be challenging.

#### 3.2.1 Graph-Based Malware Detection

Solving the problem of malware detection by examining structural and behavior qualities of applications can be seen as a compiler techniques issue. In most cases, source code is not available, so some type of decompiler is required. Additionally, compiler representations and techniques can be used to analyze an applications decompiled code. For example, DroidMiner uses static analysis to automatically mine malicious program logic from known Android malware [122]. Behavior graphs are constructed from malware in DroidMiner, and these graphs are flattened into feature vectors that are then fed into several machine learning classifiers including naive Bayes, SVM, decision trees, and random forests for malware detection. The best algorithm of DroidMiner can achieve a 95.3% detection rate on a dataset of 2466 malware. It can also reach 92% for classifying malware into its proper family.

Researchers at Los Alamos National Laboratory and the University of Technology in Iraq proposed algorithms for malware detection that make use of graphbased representations of instruction traces of binaries [13, 11]. Each graph represents a Markov Chain, where the vertices represent instructions. They use a combination of different graph kernels to construct a similarity matrix between these graphs. They then feed this resulting similarity matrix to an SVM to perform classification. These papers does not address the possibility of optimizing or parallelizing these algorithms, which exceeds  $O(n^2)$ .

Researchers at the University of Gttingen proposed a method for malware detection based on efficient embedding of Function Call Graphs (FCG), which are high level characteristics of the applications [42]. They extracted function call graphs using the Androguard framework [36]. The nodes in the graph were labeled according to the type of instructions contained in their respective functions. A neighborhood hash graph kernel was applied to evaluate the count of identical substructures in two graphs. Finally, an SVM algorithm was used for classification. In an evaluation of 12,158 malware samples, the proposed method detected 89% of the malware. The work discussed in Section 4.2 presents a similar framework that achieves higher accuracy and yields better performance due to a parallel implementation of the graph kernel used to construct the similarity matrix that is fed into the SVM [98], thus highlighting the importance of utilizing available accelerators.

#### 3.2.2 Graph Kernel Parallelization

There is a limited amount of research available that focuses on parallel implementations of graph kernels. Researchers at Stanford developed a method for implementing a parallel version of breadth-first search (BFS), and they present results on both multicore CPU and GPU [55]. They also present a hybrid method which dynamically chooses which of their implementations will yield the best performance during each BFS iteration. Although the kernel itself is different, this work shows a viable hybrid parallel implementation of a graph traversal algorithm which scales well when operating on large graphs. As discussed in Section 4.2, the hybrid implementation of SPGK is similar in nature [120], and it can be leveraged for the purpose of malware detection [98].

#### 3.3 Leveraging Heterogeneous HPC Hardware for Big Data Applications

Many applications take advantage of heterogeneous hardware using an approach known as MPI+X that leverages MPI for communication and an accelerator language (e.g., CUDA and OpenCL) or directive-based language (e.g., OpenMP and OpenACC) for computation. Codes that utilize MPI+OpenACC include: the electromagnetics code NekCEM [84], the Community Atmosphere Model - Spectral Element (CAM-SE) [81], and the combustion code S3D [71]. Codes that utilize MPI+OpenMP include computational fluid dynamics MFIX [109], Second-order Mller-Plesset perturbation theory (MP2) [62], and Molecular Dynamics [65].

Several prototype MapReduce frameworks have been specifically designed to take advantage of multi-core CPUs and GPUs: Mars [52], MapCG [54], and MATE-CG [58]. Unfortunately, they all have limitations which reduce their portability and incur a much higher programming overhead than our solution. All three prototypes are restricted to a single node or GPU, which greatly limits the size of problems that they can handle. In addition, all three prototypes use CUDA as their backend GPU language, which limits the supported hardware to only NVIDIA GPUs. Mars stores all the intermediate results in GPU memory, which requires the user to specify beforehand how much data will be emitted during the Map phase [52]. This step requires additional effort from the programmer and is highly error-prone. MapCG uses a Clike language for its Map and Reduce functions which is then converted to OpenMP and CUDA code for parallelism. This restricts the capabilities of the application to their C-like language, which doesn't support many of the advanced feature of CUDA. MATE-CG does not support a Map operation and limits the user to using only Reduce and Combine operations, which makes porting existing MapReduce applications much harder.

Researchers from Tokyo Tech present a method for scheduling Map tasks on either the CPU or GPU depending on a dynamic profile of the task [103]. Others from Ohio State created a MapReduce framework that is optimized specifically for AMDs Fusion APUs [29]. With the Fusion APU, the GPU shares the same memory space as the CPU, which enables their framework to do both pipelining and scheduling of MapReduce tasks across the CPU and GPU. Again, we see a solution that lacks portability.

#### 3.4 Wavefront Algorithm Parallelization

Wavefront-based algorithms have been in discussion over the past approximately 30 years. The wavefront method was revisited in [117] using loop skewing, a procedure to derive the wavefront method of execution of nested loops. Considered as far back as 1974 by Lamport [69], wavefront computations have had applications to diverse areas including linear equation solvers [72, 87], gene sequence alignment [104] and radiation transport [64, 17], iterative solution methods [91], particle physics simulations [63], and parallel solution of triangular of systems of linear equations [53].

State-of-the-art research shows wavefront parallelization on GPUs, FPGAs and co-processors. Smith Waterman, a dynamic programming concept and a local sequence alignment algorithm, expresses wavefront-based computations and the algorithm has been mapped to NVIDIA GPUs [94], on Cell BE [116] and on reconfigurable computing platforms [124, 25]. ASCI Sweep3D wavefront application solves a 1-group time-independent discrete ordinates neutron transport problem on IBM Blue Gene/P machine [57] by using blocking techniques for better parallel efficiency as the application undergoes rapid succession of wavefronts. Preliminary studies to use TBB, Cilk, CnC, and OpenMP 3.0 for wavefront in [37] indicate that optimizations be wrapped in a higher level template to make it easier for less experienced users. AWE Chimaera [80], NAS-LU [16] use different implementations of Lamport's original parallel pipelined wavefront 'hyperplane' algorithm [69]. Acceleration of generalized pipeline wavefront applications on modern GPU is discussed in [86]. Geometric Multigrid (GMG) is a class of algorithm used to accelerate the convergence of iterative solvers for linear systems [114] using wavefront techniques. Proxy apps such as KRIPKE [5], SNAP [8] (mimicking communication patterns of PARTISN [19] transport code) wavefront codes investigate different data layout patterns and parallelism. A one-sided communication in Sweep3D using Coarray Fortran achieved comparable performance to that of the MPI version [33].

Classic compiler approaches for wavefront shows loop skewing followed by loop permutation, where skewing breaks a dependence that would otherwise prevent permute; this is implemented within CHiLL [28], a polyhedral compiler transformation framework. Other work includes IEGenLib [108], Codegen+ [26]. A recent paper [110] presents compiler and runtime framework within polyhedral framework to automatically generate wavefront parallelization of sparse matrix computations. Swift/T [118] has also been used to express wavefront computations [15]. Automatic generation of wavefront parallelization of sparse matrix computations was discussed in [110]. Wavefront parallelization of Gauss-Seidel and related algorithms employ manually written inspectors and executors as discussed in [107, 45]. High Productive Computing System (HPCS) languages: Chapel [23], X10 [79] and Fortress [12] also aim to provide users with better programmability and productivity but they do not offer enough abstractions or vocabulary for heterogeneous platforms. HTP [121] proposed a hierarchical tree place that maps to an architecture with the goal of scheduling tasks to different different nodes in the tree.

All these prior studies indicate that this is an important problem to solve and that there are different types of approaches to approach this problem. However, most of these strategies cannot be easily adopted for large scale applications since they are either not solving the wavefront problem itself but offering solutions to a specific problem type, requiring the user to incur a steep learning curve, or providing a solution that is confined to a particular compiler and/or hardware. Such gaps in the state-ofthe-art work served as a motivation for us to rethink this problem and develop a suitable solution that will provide scientific developers with directives supported by appropriate loop transformation algorithms addressing the wavefront problem.

#### Chapter 4

#### MOTIVATION FOR USING ACCELERATORS

Prior to investigating high-level complex parallel patterns, the author studied related topics including auto-tuning high-level languages targeting heterogeneous systems, parallelizing machine learning algorithms used for malware detection, and combining MapReduce with on-node parallel programming frameworks in order to accelerate Big Data applications. This chapter dives into those topics, provides some insight into the authors related contributions in the field of high performance computing, and highlights the benefits of using accelerators in the associated domains.

## 4.1 Auto-Tuning GPU Accelerated Applications Using High-Level Languages

Determining the best set of optimizations to apply to a kernel to be executed on the graphics processing unit (GPU) is a challenging problem. There are large sets of possible optimization configurations that can be applied, and many applications have multiple kernels. Each kernel may require a specific configuration to achieve the best performance, and moving an application to new hardware often requires a new optimization configuration for each kernel.

This work applies optimizations to GPU code using HMPP and OpenACC, which are high-level directive-based languages backed by source-to-source compilers that can generate GPU code based on annotations in portions of the host code. However, programming with high-level languages was previously thought to mean a loss of performance compared to using low-level languages. This work shows that it is possible to improve the performance of a high-level language by using auto-tuning. We perform auto-tuning on a large optimization space on GPU kernels, focusing on loop permutation, loop unrolling, tiling, and specifying which loop(s) to parallelize, and show results on convolution kernels, codes in the PolyBench suite, and computationally expensive kernels extracted from the QuantLib library, which is widely used in the domain of computational finance. The results show that our auto-tuned implementations are significantly faster than the default HMPP and OpenACC implementations and can meet or exceed the performance of manually coded CUDA / OpenCL implementations [46, 47].

Figure 4.1: Single precision speedup graph comparing the performance of auto-tuned HMPP code against manually written CUDA code

Figure 4.1 shows a sample of the results obtained using HMPP to auto-tune kernels from the Polybench benchmark suite [46]. We see that the HMPP auto-tuned code is at least on par with manually written and tuned CUDA code in all cases, and in some cases, it exceeds the performance of the CUDA code by a considerable margin. This demonstrates the viability of high-level languages from a performance standpoint, in addition to the benefits of their programmability and inherent portability.

## 4.2 Parallelization of Graph-Based Machine Learning for Malware Detection

Prior work in learning-based malware detection engines primarily focuses on dynamic trace analysis and byte-level n-grams. The approach in this work differs in that compiler intermediate representations are used, i.e., the call-graph representation of binaries. Using graph-based program representations for learning provides structure of the program, which can be used to learn more advanced patterns.

Figure 4.2: Figure 4.2a shows the workflow toward construction of a machine learning model generated during this work's training phase. Figure 4.2b shows a flow diagram demonstrating the classification of an unseen binary application used during the eval-

uation phase.

This work uses a computationally expensive graph kernel to identify similarities between call graphs extracted from binaries [98]. The output similarity matrix is fed into a Support Vector Machine (SVM) algorithm to construct highly-accurate models to predict whether a binary is malicious or not, as shown in Figure 4.2a. Once a model has been constructed, similarity vectors for call graphs of unknown applications need to be computed in order to feed into the model for comparison against the training data set. This is known as the testing phase, as shown in Figure 4.2b. Since this graph kernel is computationally expensive due to the size of the input graphs, different parallelization methods for CPUs and GPUs are evaluated to speed up this kernel, allowing continuous construction of up-to-date models in a timely manner. The hybrid implementation presented, which leverages both CPU and GPU, yields the best performance, achieving up to a 14.2x improvement over an already optimized OpenMP version, as shown in Table 4.1. The generated graph-based models are then compared to previously state-of-the-art feature vector 2-gram and 3-gram models on a dataset consisting of over 22,000 binaries. This work's classification accuracy using graphs is over 19% higher than either n-gram model and gives a false positive rate of less than 0.1%. It is also possible to consider large call graphs and dataset sizes because of the reduced execution time of the parallelized graph kernel implementation, which leads to the construction of more accurate prediction models.

| Dataset | GPU 1D            |                    | Ope     | Hybrid             |                    |

|---------|-------------------|--------------------|---------|--------------------|--------------------|

| Size    |                   | Overlap            | Matrix  | Graph              | пурпа              |

| 6K      | $1.58 \mathrm{h}$ | $40.52~\mathrm{m}$ | 1.01 m  | $3.19 \mathrm{~m}$ | 4.65 s             |

|         | 0.01x             | 0.03x              | 1.0x    | 0.35x              | 14.2x              |

| 12K     | 9.36 h            | $5.61 \mathrm{h}$  | 10.96 m | 20.48 m            | $52.57~\mathrm{s}$ |

| 121     | 0.02x             | 0.03x              | 1.0x    | 0.53x              | 12.5x              |

| 21K     |                   |                    | 4.55  h | $5.50 \ h$         | $50.37 \mathrm{m}$ |

| 211     | me                | mory               | 1.0x    | 0.83x              | 5.42x              |

| 22K     | exhausted         |                    | 6.51 h  | 12.24 h            | 2.47 h             |

|         |                   |                    | 1.0×    | 0.53x              | 2.63x              |

Table 4.1: Comparing similarity matrix computation time for each dataset. Runtimes (h: hours, m: minutes, s: seconds) are presented for each implementation. Below each runtime we give speedup compared to the best OpenMP (OpenMP Matrix) implementation is shown. VRAM limitation was exceeded for our larger datasets when only running on the GPU.

Despite the excellent performance achieved utilizing this novel approach to machine learning applied to malware detection, the hybrid implementation presented is not portable due to the use of architecture-specific programming models (such as CUDA). At the time when this work was presented, there were no high-level tools available that were suitable for abstracting a complex graph kernel like the one used. This presented a significant implementation challenge because this approach needed to be rewritten in order to run on the GPU. However, it still offered insights as to how certain types of algorithms behave on different parallel architectures. We found that on average, smaller graphs were better compared using the CPU and larger graphs, whose computational cost drastically outweighed the overhead of data movement, were better suited for execution on the GPU.

# 4.3 A Portable, High-Level Graph Analytics Paradigm Targeting Distributed, Heterogeneous Systems

This paper presents a portable, high-level paradigm that can be used to run Big Data applications on existing and future HPC systems. More specifically, it targets graph analytics applications, since these types of applications are becoming increasingly more popular in the Big Data and Machine Learning communities. Using this paradigm, we accelerate three real-world, compute and data intensive, graph analytics applications: a function call graph similarity application (similar to the one discussed in Section 4.2), a triangle enumeration subroutine, and a graph assaying application.

Our paradigm utilizes the popular MapReduce framework, Apache Spark, in conjunction with an on-node computational framework (in our case CUDA) in order to simultaneously take advantage of automatic data distribution and specialized hardware present on each node of our HPC systems, as shown in Figure 4.3. We demonstrate scalability with regard to compute intensive portions of the code that are parallelizable, as well as an exploration of the parameter space for each application. We present results on a heterogeneous (hybrid) cluster with a variety of CPUs (from both Intel and AMD) and GPUs (from both AMD and NVIDIA), as well as NVIDIAS PSG cluster, which is homogeneous and utilizes NVIDIAs next-generation P100 GPUs. Figure 4.4 presents performance results for the graph assaying application when run on a heterogeneous cluster consisting of a variety of CPUs and GPUs. It exhibits favorable scalability when run across multiple nodes, and a considerable speedup when using the GPU instead of the CPU on those nodes for their portion of the computation. These results prove that

Figure 4.3: A high-level depiction of the proposed paradigm, which uses Spark for data/task distribution in conjunction with a local computational framework (X) on each node.

our method yields a portable solution that can be used to leverage almost any legacy, current, or next-generation HPC or cloud-based system [97, 101].

This work aimed to tackle the challenges of automating the process of task distribution across nodes in an HPC system, and it redefined the way we think about portability by running real-world graph analytics applications across a cluster composed of a range of different parallel architectures, while achieving optimal load balancing. To our knowledge, this is the first work to combine and efficiently utilize legacy, state-of-the-art, and next-generation hardware simultaneously in an abstract fashion.

Figure 4.4: Runtime results for Graph Assaying run on the hybrid cluster

# 4.4 Summary

In short, these projects all contributed to our understanding of HPC systems, in regards to both parallel hardware architectures and the software programming models used to harness the power of such hardware. The skills we have acquired in overcoming the obstacles faced in each work provides the foundation needed to tackle a multifaceted problem like the one described in this thesis. In order to accomplish the goal of creating a portable programming abstraction for the wavefront parallel pattern, we need to use these skills to understand how the pattern in question behaves on different types of hardware, identify the challenges in abstracting the pattern such that it will be performant across existing and future parallel architectures, and understand the needs of parallel application developers in order to develop extensions that are easy to use from a development perspective.

#### Chapter 5

# EXPLORING A COMPLEX PARALLEL PATTERN: WAVEFRONT

This section introduces the complex parallel pattern investigated by this thesis, demonstrate it's real-world impact, discuss the obstacles faced when attempting to parallelize such a pattern, and outline our goals moving forward.

#### 5.1 Wavefront Parallel Patterns

A wavefront parallel pattern is a type of complex parallel pattern that is not easily representable in existing high-level parallel programming models due to its irregular, multi-dimensional data dependencies. This pattern is used to examine a multidimensional space that is split into components called *gridcells*. Each gridcell contains elements that require some sort of in-gridcell computation, allowing for parallelism across these gridcells. However, the complexity in implementing this type of parallel computation arises due to the upstream data dependencies between gridcells. Wavefront patterns exhibit a directional behavior in that the result computed at each gridcell depends on the result computed at each of its neighboring gridcells along each axis in the multi-dimensional space. This dependency places a restriction on the order in which results can be computed. A parallel wavefront implementation sorts these in-gridcell computations into a series of ordered *wavefronts* described by a sequence of planes of gridcells starting at a corner of the multi-dimensional grid and sweeping through the whole grid.

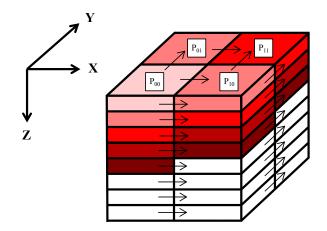

An example of the 3-dimensional wavefront sweep ordering used in Minisweep is shown in Figure 5.1. While other orderings are allowed insofar as the upstream data dependencies are satisfied, this is generally deemed to be the most efficient way

Figure 5.1: Minisweep's wavefront computational pattern

of parallelizing a wavefront-based pattern. It is worth noting that there are some variations in upstream data dependency behavior across different wavefront algorithms.