## Reduced lattice temperature high-speed operation of pseudomorphic InGaAs/GaAs field-effect transistors

J. Laskar, S. Maranowski, S. Caracci, M. Feng, and J. Kolodzey<sup>a)</sup>

Center for Compound Semiconductor Microelectronics and Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801

(Received 3 June 1991; accepted for publication 30 August 1991)

This letter presents a detailed study of the temperature dependence of submicron pseudomorphic InGaAs on GaAs substrate modulation doped field-effect transistors (MODFETs), doped-channel metal insulator field effect transistors (MISFETs), and metal semiconductor field-effect transistors (MESFETs). We determine similar variation in the measured extrinsic current gain cutoff frequency,  $F_T$ , and similar dependencies of the effective electron velocity,  $v_{\rm eff}$ , with reduced lattice temperature for the different field-effect transistors. The  $v_{\rm eff}\sim T^{-b}$  where 0.15 < b < 0.20 over the temperature range of 300 to 110 K. These results provide direct experimental evidence that the saturated velocity of electrons is the most important parameter for high-speed operation and with proper design these different pseudomorphic InGaAs/GaAs field-effect transistors provide similar potential for high-speed operation.

The advent of a reproducible cryogenic microwave measurement system<sup>1</sup> has allowed for detailed studies of the reduced lattice temperature operation of pseudomorphic InGaAs/GaAs field-effect transistors (FETs). Recent results include cryogenic high-speed measurements of doped channel metal insulator field-effect transistors (MISFETs),<sup>2</sup> modulation doped field effect transistors (MODFETs),<sup>3</sup> and metal semiconductor field-effect transistors (MESFETs). 4,5 The MODFET is attractive for the enhanced electron mobility achieved by reduced ionized impurity scattering as the result of spatially separating the electrons from the ionized donors. The doped channel MISFET is distinguished by a narrow-gap active channel and undoped wide-gap insulator, which is opposite to the MODFET doping scheme. The advantages of this device design includes higher current drivability and higher breakdown voltage. The MESFET is attractive since donors can be directly ion implanted into the substrate increasing the potential for high manufacturing throughput and reliability. A surprising trend, however, has been the similar high-speed performance of the different FETs for gate lengths from 1.0 to 0.1  $\mu$ m. The recent results in the literature raises the question of how significant are the contributions of high-electron mobility and two-dimensional electron transport in the high-speed operation of InGaAs/ GaAs FET performance.

In this letter we report a detailed study of the temperature dependence of pseudomorphic InGaAs on GaAs substrate MODFETs, doped-channel MISFETs, and MESFETs. We determined similar increases in the measured extrinsic  $F_T$  and similar dependances of the effective electron velocity,  $v_{\rm eff}$ , with reduced lattice temperature for the different FETs.

The MODFET structure used in this study was grown

2412

by solid-source molecular beam epitaxy (MBE) and consists of a 1 µm GaAs buffer, 170 Å In<sub>0.2</sub>Ga<sub>0.8</sub>As strained channel, 50 Å undoped Al<sub>0.25</sub>Ga<sub>0.75</sub>As undoped spacer, δdoped Si plane with areal density  $7 \times 10^{12}$  cm<sup>-2</sup>, 350 Å undoped  $Al_{0.25}Ga_{0.75}As$  insulator, and a 200 Å cap layer of n-GaAs Si doped to  $2.7\times10^{18}$  cm  $^{-3}$ . The MESFET was grown by metalorganic chemical vapor deposition and consists of an undoped 600 Å In<sub>0.18</sub>Ga<sub>0.82</sub>As layer, and an undoped 1000-Å-thick layer of In<sub>v</sub>Ga<sub>1-v</sub>As with the In composition graded from 0.18 to 0 at the surface for an improved Schottky barrier height. The active channel of the MESFET is formed by ion implanted Si + 29 ion species and subsequent capless annealing at 850 °C for 20 min. The peak carrier concentration in the channel is  $2 \times 10^{18}$ cm<sup>-3</sup>. The doped channel MISFET was grown by solid source MBE and consists of a 1  $\mu$ m GaAs buffer, 150 Å  $In_{0.3}Ga_{0.7}As$  strained channel Si doped to  $3 \times 10^{18}$  cm<sup>-3</sup>, 250 Å undoped Al<sub>0.35</sub>Ga<sub>0.65</sub>As insulator, and a 200 Å cap layer of *n*-GaAs Si doped to  $5 \times 10^{18}$  cm<sup>-3</sup>.

An electron-beam direct write process has been used to define "T-shaped" gates with device isolation achieved by wet chemical etching. The MESFETs in this study have gate dimensions of  $0.25\times200~\mu\mathrm{m}$  and  $0.5\times200~\mu\mathrm{m}$  with a source-drain spacing of 2  $\mu\mathrm{m}$ . The MODFETs have gate dimensions of  $0.35\times100~\mu\mathrm{m}$  and  $0.47\times100~\mu\mathrm{m}$  with a source-drain spacing of 1  $\mu\mathrm{m}$ . The MISFETs have gate dimensions of  $0.25\times100~\mu\mathrm{m}$  with a source-drain spacing of  $1~\mu\mathrm{m}$ .

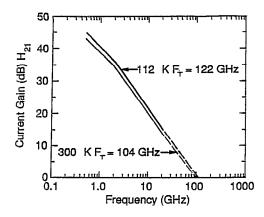

S-parameter data was collected from 0.5 to 26.5 GHz using a Hewlett-Packard 8510 B network analyzer. Measurements have been made at a temperature of 300 K using a Cascade model 42 D high-frequency probe station and at 110 K using a custom-built cryogenic high-frequency probe station. Calibrations were performed "off-water" using an impedance standard substrate from Cascade Microtech. The measured s parameters are used to calculate the h parameters. In Fig. 1, we plot typical  $|h_{21}|$  versus

<sup>&</sup>lt;sup>a)</sup>Present address: Department of Electrical Engineering, University of Delaware, Newark, DE 19716.

FIG. 1. Plot of the forward short-circuit current gain  $h_{21}$  vs frequency at 300 and 112 K for a In<sub>y</sub>Ga<sub>1-y</sub>As graded channel MESFET (Ref. 4). The gate dimensions are  $0.25\times200~\mu\mathrm{m}$  and the  $F_T$  increases from 104 to 122 GHz when the lattice temperature is reduced from 300 to 112 K.

frequency results for a  $0.25\times200~\mu\mathrm{m}$  InGaAs/GaAs MESFET at 300 and 112 K. We observe no evidence of resonance or inductive effects and the current gain follows a -6 dB/octave roll-off which extrapolates to the unity short-circuit current gain cut-off frequency,  $F_T$ . The measured peak  $F_T$  improves from 104 to 122 GHz when the lattice temperature is reduced from 300 to 112 K.

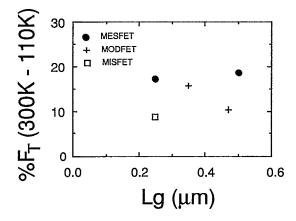

In Fig. 2, we plot the typical percentage change from 300 to 110 K in the extrinsic  $F_T$  for the three FET structures for gate lengths between 0.5 and 0.25  $\mu$ m. When the effect of pad parasitics is removed the percentage increase in  $F_T$  is less than 30% for all devices. The peak  $F_T$  at 300 K is 104 GHz for the MESFET, 88 GHz for the MODFET, and 56 GHz for the doped channel MISFET.

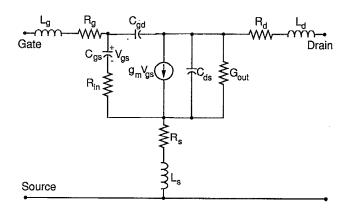

A detailed analysis of the extrinsic s parameters has been made to extract the intrinsic device parameters. It is important to extract the intrinsic device parameters to accurately measure the trends of important physical parameters for different device structures and different lattice temperatures. The hybrid- $\pi$  equivalent circuit of Fig. 3 was used to fit the measured s parameters. The circuit analysis technique originally proposed in Ref. 7 is used to help to

FIG. 2. Plot of the typical percentage increase in the measured  $F_T$  vs gate length for the InGaAs/Gas MODFETs, doped channel MISFETs, and MESFETs studied.

FIG. 3. Schematic of the hybrid- $\pi$  circuit model used to fit the measured s parameters and validate the extracted small-signal circuit element values.

uniquely identify the small-signal element values. The pad parasitics were determined by measuring a gateless device with the technique outlined in.<sup>8</sup>

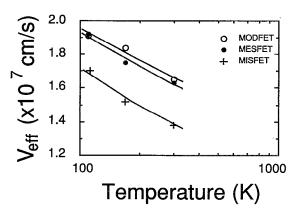

Once the small-signal element values have been determined and the values validated by fitting to the equivalent circuit of Fig. 3 we estimate an effective electron velocity,  $v_{\rm eff}$ , from:

$$v_{\text{eff}} = L_g \frac{g_m}{C_{gs} + C_{dg}}.$$

(1)

The  $v_{\rm eff}$  is then plotted versus temperature in Fig. 4. Hall-effect measurements for the MODFETs used in this study show that the electron mobility increases by a factor of five when the lattice temperature is reduced from 300 to 77 K. The electron mobility decreases by 2% in the doped channel MISFET and decreases by 7% in the MESFET. Independent determination for 5% indium channel MODFETs have shown a saturated velocity increase of 20% when the lattice temperature is reduced from 300 to 100 K. These results are important for they provide direct experimental evidence that the low-field electron mobility is not the dominant factor in determining the high-speed performance of InGaAs/GaAs FETs. Similar conclusions about

FIG. 4. Plot of the extracted effective electron velocity,  $v_{\rm eff}$ , vs  $L_g$  for the InGaAs/GaAs FETs studied. The  $v_{\rm eff} \sim T^{-b}$  where 0.15 < b < 0.20 over the temperature range of 300 to 110 K.

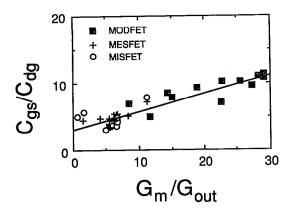

FIG. 5. Plot of the ratio of  $C_{\rm gs}/C_{\rm gd}$  vs  $g_m/g_{\rm out}$  for all InGaAs/GaAs FETs measured in this study. The data include results over the temperature range of 300–110 K. The measured data fit well to a slope,  $\beta$ , of -0.27 which agrees well with 300 K results reported in Ref. 11.

the relevance of electron mobility for high-speed performance have been drawn from recent results in the literature. 4,10

To gain insight into the physical mechanisms controlling high-speed operation we have applied a feedback correlation analysis as originally proposed in Ref. 11:

$$C_{\rm gg}/C_{\rm gd} = 1 + \beta g_m/g_{\rm out} \tag{2}$$

where  $C_{\rm gs}$  is the gate-source capacitance,  $C_{\rm gd}$  is the draingate capacitance,  $g_m$  is the transconductance,  $g_{\rm out}$  is the output conductance, and  $\beta$  is an empirical fitting parameter. We can determine the parameter  $\beta$  by plotting  $C_{\rm gs}/C_{\rm gd}$  versus  $g_m/g_{\rm out}$ . Since  $g_{\rm out}$  increases as current spreads out of the conducting channel, and  $g_m$  represents control of the channel current, the ratio  $g_m/g_{\rm out}$  is a measure of the confinement of rf current. A small value of  $\beta$  results in a large  $g_m/g_{\rm out}$  ratio reflecting good current confinement in the drift region of the device (high-voltage gain and small output conductance).

In Fig. 5 we plot  $C_{\rm gs}/C_{\rm gd}$  versus  $g_m/g_{\rm out}$  for the three different FETS for several different devices over a temperature range from 300 to 110 K. We find  $\beta = 0.27$  for all the devices over the temperature range 300 to 100 K which agrees quite well with the value of  $\beta \sim 0.3$  extracted in Ref. 11 for 300 K measurements. This analysis not only con-

firms the previous trends observed in the literature<sup>4</sup> but also reveals that there is no enhanced carrier confinement under high fields at reduced lattice temperatures for these InGaAs/GaAs FETs.

In conclusion, based on detailed cryogenic microwave pseudomorphic InGaAs/GaAs measurements of MODFETs, doped channel MISFETs, and MESFETs we find a similar variation of  $v_{\text{eff}}$  with temperature. Because of the high-electric fields associated with submicron FET operation the saturated velocity of electrons in the gate-drain portion of the transistor is the most important parameter for high-speed operation. We find no evidence of enhanced carrier confinement in either reduced lattice temperature operation or in the two-dimensional quantum well structures. These results provide direct experimental evidence that with proper device design these different pseudomorphic InGaAs/GaAs FET structures all provide good potential for high-speed operation.

The authors would like to thank A. Ketterson and I. Adesida for assistance with device processing, J. Baillargeon and K. Y. Cheng for assistance with material growth, and Cascade Microtech and Hewlett-Packard for equipment donations. This work is supported by NSF Grant No. EET 87-19100, NSF-CDR-43166, JSEP-N00014-84C-0149, and AT&T Affiliates 52.

2414

<sup>&</sup>lt;sup>1</sup>J. Laskar and J. Kolodzey, J. Vac. Sci. Technol. B 8, 1161 (1990).

<sup>&</sup>lt;sup>2</sup>J. Laskar, J. Kolodzey, A. A. Ketterson, I. Adesida, and A. Y. Cho, IEEE Electron Device Lett. EDL-11, 300 (1990).

<sup>&</sup>lt;sup>3</sup> J. Laskar, J. Kolodzey, A. A. Ketterson, S. Caracci, and I. Adesida, Cryogenics **30**, 1134 (1990).

<sup>&</sup>lt;sup>4</sup>M. Feng, J. Laskar, W. Miller, J. Kolodzey, G. E. Stillman, and C. L. Lau, Appl. Phys. Lett. **58**, 2690 (1991).

<sup>&</sup>lt;sup>5</sup>S. Maranowski, J. Laskar, M. Feng, and J. Kolodzey, Electron Device Lett. (to be published).

<sup>&</sup>lt;sup>6</sup>M. Feng, C. L. Lau, V. Eu, and C. Ito, Appl. Phys. Lett. **57**, 1233 (1990).

<sup>&</sup>lt;sup>7</sup>G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, IEEE Trans. Microwave Theory Tech. MTT-36, 1151 (1988).

<sup>&</sup>lt;sup>8</sup>P. J. van Wijen, H. R. Claessen, and E. A. Woisheimer, *Proc. of IEEE Bipolar Ckts. and Tech. Meeting, Minneapolis, 1987* (IEEE, New York, 1987), p. 70.

<sup>&</sup>lt;sup>9</sup>J. Dickmann, C. H. Heedt, and H. Daembkes, IEEE Trans. Electron Dev. 36, 2315 (1989).

<sup>&</sup>lt;sup>10</sup> M. V. Fischetti and S. E. Laux, IEEE Trans. Electron Devices 38, 650 (1991).

<sup>&</sup>lt;sup>11</sup> E. Kohn, Inst. Phys. Conf. Ser., **112**, 411 (1990).