# Instruction Selection and Scheduling

#### The Problem

Writing a compiler is a lot of work

- Would like to reuse components whenever possible

- Would like to automate construction of components

- Front end construction is largely automated

- Middle is largely hand crafted

- (Parts of) back end can be automated

#### Definitions

#### Instruction selection

- Mapping <u>IR</u> into assembly code

- Assumes a fixed storage mapping & code shape

- Combining operations, using address modes

#### Instruction scheduling

- Reordering operations to hide latencies

- Assumes a fixed program (set of operations)

- Changes demand for registers

#### Register allocation

- Deciding which values will reside in registers

- Changes the storage mapping, may add false sharing

- Concerns about placement of data & memory operations

### The Problem

# Modern computers (still) have many ways to do anything

Consider register-to-register copy in Iloc

- Obvious operation is  $i2i r_i \Rightarrow r_j$

- Many others exist

| addI  | $r_{i}, 0 \Rightarrow r_{j}$ | subI $r_{i}, 0 \Rightarrow r_{j}$      | lshiftI $r_i, 0 \Rightarrow r_j$ |

|-------|------------------------------|----------------------------------------|----------------------------------|

| multI | $r_{i},1 \Rightarrow r_{j}$  | divI $r_{i}$ , 1 $\Rightarrow$ $r_{j}$ | rshiftI $r_i, 0 \Rightarrow r_j$ |

| orI   | $r_{i}, 0 \Rightarrow r_{j}$ | $xorI r_i, 0 \Rightarrow r_j$          | and others                       |

# The Problem

Modern computers (still) have many ways to do anything

- Human would ignore all of these

- Algorithm must look at all of them & find lowcost encoding

- → Take context into account (busy functional unit?)

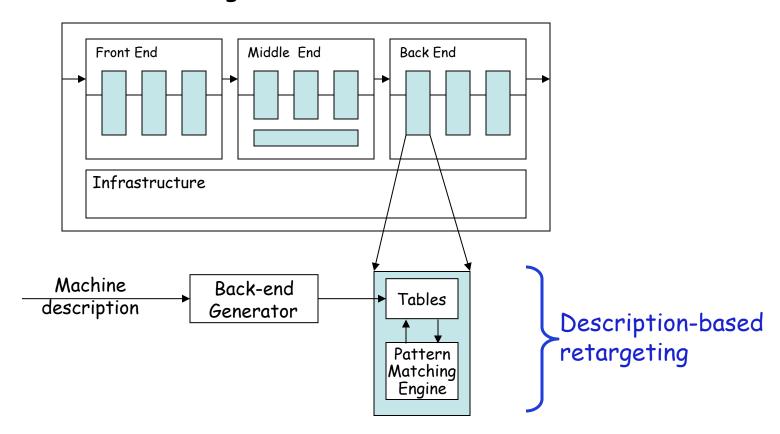

Want to automate generation of instruction selectors

Machine description can help with scheduling & allocation

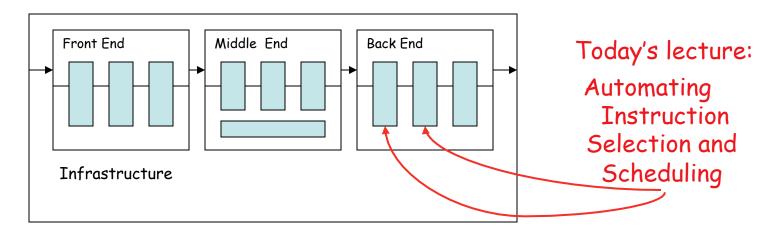

# The Big Picture

# Need pattern matching techniques

- Must produce good code (some metric for good)

- Must run quickly

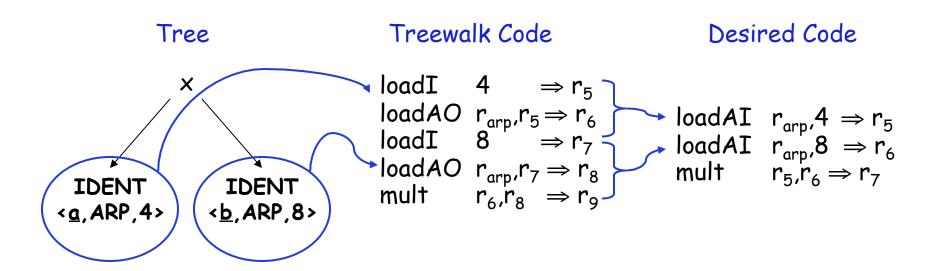

A treewalk code generator runs quickly How good was the code?

# IDENT IDENT

Tree

#### Treewalk Code

#### Desired Code

$$\begin{array}{ll} \text{loadAI} & r_{\text{arp}}\text{,4} \Rightarrow r_5 \\ \text{loadAI} & r_{\text{arp}}\text{,8} \Rightarrow r_6 \\ \text{mult} & r_5\text{,r}_6 \Rightarrow r_7 \end{array}$$

#### Need pattern matching techniques

- Must produce good code

- Must run quickly

(some metric for good)

A treewalk code generator runs quickly How good was the code?

#### Tree-oriented IR

# Suggests pattern matching on trees

- Tree-patterns as input, matcher as output

- Each pattern maps to a target-machine instruction sequence

- Use bottom-up rewrite systems

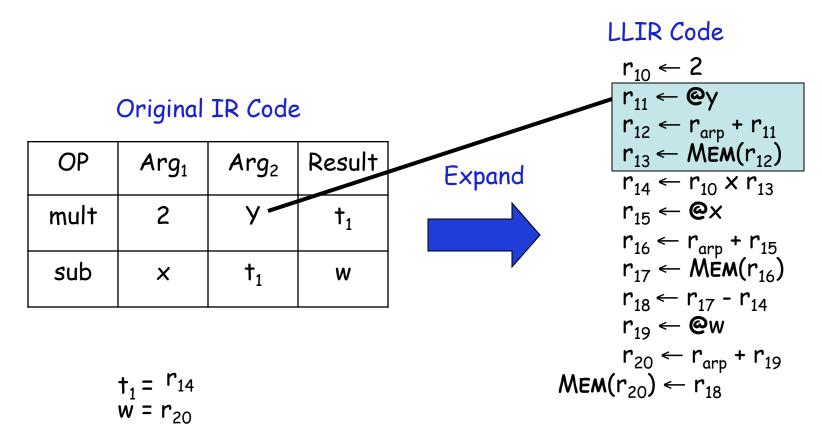

#### Linear IR

Suggests using some sort of string matching

- Strings as input, matcher as output

- Each string maps to a target-machine instruction sequence

- Use text matching or peephole matching

- Basic idea

- Compiler can discover local improvements locally

- → Look at a small set of adjacent operations

- → Move a "peephole" over code & search for improvement

- Classic example: store followed by load

# Original code

$$\begin{array}{ll} \text{storeAI} & r_1 \Rightarrow r_{\text{arp}}, \\ \text{loadAI} & r_{\text{arp}}, 8 \Rightarrow r_{15} \end{array}$$

# Improved code

$$\begin{array}{lll} \text{storeAI} & r_1 \Rightarrow r_{\text{arp}}\text{,8} & \text{storeAI} & r_1 \Rightarrow r_{\text{arp}}\text{,8} \\ \text{loadAI} & r_{\text{arp}}\text{,8} \Rightarrow r_{15} & \text{i2i} & r_1 \Rightarrow r_{15} \end{array}$$

- Basic idea

- Compiler can discover local improvements locally

- → Look at a small set of adjacent operations

- → Move a "peephole" over code & search for improvement

- Classic example: store followed by load

- Simple algebraic identities

# Original code

$$\begin{array}{ll} \text{addI} & r_2\text{,0} \Rightarrow r_7 \\ \text{mult} & r_4\text{,}r_7 \Rightarrow r_{10} \end{array}$$

# Improved code

mult

$$r_4,r_2 \Rightarrow r_{10}$$

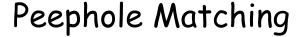

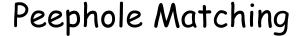

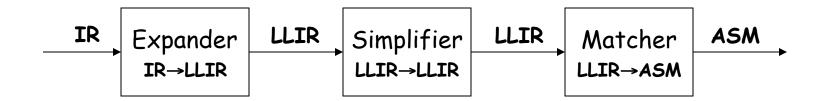

# Peephole Matching

- Basic idea

- Compiler can discover local improvements locally

- → Look at a small set of adjacent operations

- → Move a "peephole" over code & search for improvement

- Classic example: store followed by load

- Simple algebraic identities

- Jump to a jump

# Original code

jumpI

$$\rightarrow L_{10}$$

: jumpI  $\rightarrow L_{11}$

Improved code

$$L_{10}$$

: jump  $I \rightarrow L_{11}$

#### Implementing it

- Early systems used limited set of hand-coded patterns

- Window size ensured quick processing

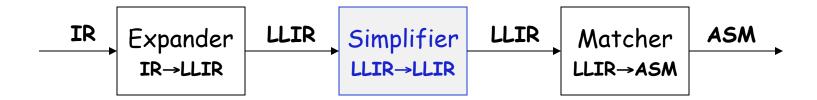

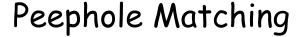

#### Modern peephole instruction selectors

Break problem into three tasks

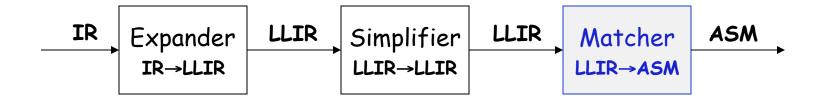

#### Expander

- Turns IR code into a low-level IR (LLIR)

- Operation-by-operation, template-driven rewriting

- Significant, albeit constant, expansion of size

# Peephole Matching

#### Simplifier

- Looks at LLIR through window and rewrites is

- Uses forward substitution, algebraic simplification, local constant propagation, and dead-effect elimination

- Performs local optimization within window

- This is the heart of the peephole system

- → Benefit of peephole optimization shows up in this step

#### Matcher

- Compares simplified LLIR against a library of patterns

- Picks low-cost pattern that captures effects

- Generates the assembly code output

| OP     | Arg <sub>1</sub> | Arg <sub>2</sub> | Result         |

|--------|------------------|------------------|----------------|

| mult - | 2                | У                | † <sub>1</sub> |

| sub    | ×                | †1               | w              |

$$t_1 = r_{14}$$

$w = r_{20}$

#### LLIR Code

$$r_{10} \leftarrow 2$$

$r_{11} \leftarrow \mathbf{@} \mathbf{y}$

$$\mathbf{r}_{12} \leftarrow \mathbf{r}_{arp} + \mathbf{r}_{11}$$

$$r_{13} \leftarrow MEM(r_{12})$$

$$r_{14} \leftarrow r_{10} \times r_{13}$$

$$r_{15} \leftarrow ex$$

Expand

$$r_{16} \leftarrow r_{arp} + r_{15}$$

$$r_{17} \leftarrow MEM(r_{16})$$

$$r_{18} \leftarrow r_{17} - r_{14}$$

$$r_{19} \leftarrow @w$$

$$r_{20} \leftarrow r_{arp} + r_{19}$$

$$\mathsf{MEM}(\mathsf{r}_{20}) \leftarrow \mathsf{r}_{18}$$

# Original IR Code

| OP   | Arg <sub>1</sub> | Arg <sub>2</sub> | Result         |

|------|------------------|------------------|----------------|

| mult | 2                | У                | † <sub>1</sub> |

| sub  | ×                | †1               | W              |

$\bar{w} = r_{20}$

Expand

#### LLIR Code

$$r_{10} \leftarrow 2$$

$$r_{11} \leftarrow e_y$$

$$r_{12} \leftarrow r_{arp} + r_{11}$$

$$r_{13} \leftarrow MEM(r_{12})$$

$$r_{14} \leftarrow r_{10} \times r_{13}$$

$$r_{15} \leftarrow ex$$

$$r_{16} \leftarrow r_{arp} + r_{15}$$

$$r_{17} \leftarrow M\dot{E}M(r_{16})$$

$$r_{18} \leftarrow r_{17} - r_{14}$$

$$r_{19} \leftarrow @w$$

$$r_{20} \leftarrow r_{arp} + r_{19}$$

$$\mathsf{MEM}(\mathsf{r}_{20}) \leftarrow \mathsf{r}_{18}$$

#### LLIR Code

$$r_{10} \leftarrow 2$$

$r_{11} \leftarrow \mathbf{ey}$

$r_{12} \leftarrow r_{arp} + r_{11}$

$r_{13} \leftarrow \mathbf{MEM}(r_{12})$

$r_{14} \leftarrow r_{10} \times r_{13}$

$r_{15} \leftarrow \mathbf{ex}$

$r_{16} \leftarrow r_{arp} + r_{15}$

$r_{17} \leftarrow \mathbf{MEM}(r_{16})$

$r_{18} \leftarrow r_{17} - r_{14}$

$r_{19} \leftarrow \mathbf{ew}$

$r_{20} \leftarrow r_{arp} + r_{19}$

$\mathbf{MEM}(r_{20}) \leftarrow r_{18}$

$$\begin{aligned} \text{LLIR Code} \\ r_{13} &\leftarrow \text{MEM}(r_{\text{arp}} + \text{@y}) \\ r_{14} &\leftarrow 2 \times r_{13} \\ r_{17} &\leftarrow \text{MEM}(r_{\text{arp}} + \text{@x}) \\ r_{18} &\leftarrow r_{17} - r_{14} \end{aligned}$$

$$\text{MEM}(r_{\text{arp}} + \text{@w}) \leftarrow r_{18}$$

$$\begin{array}{c} \text{LLIR Code} \\ r_{13} \leftarrow \text{MEM}(r_{\text{arp}} + \text{@y}) \\ r_{14} \leftarrow 2 \times r_{13} \\ r_{17} \leftarrow \text{MEM}(r_{\text{arp}} + \text{@x}) \\ r_{18} \leftarrow r_{17} - r_{14} \end{array} \qquad \begin{array}{c} \text{Match} \\ \text{loadAI} \quad r_{\text{arp}}, \text{@y} \Rightarrow r_{13} \\ \text{multI} \quad 2 \times r_{13} \Rightarrow r_{14} \\ \text{loadAI} \quad r_{\text{arp}}, \text{@x} \Rightarrow r_{17} \\ \text{sub} \quad r_{17} - r_{14} \Rightarrow r_{18} \\ \text{storeAI} \quad r_{18} \quad \Rightarrow r_{\text{arp}}, \text{@w} \end{array}$$

- Introduced all memory operations & temporary names

- Turned out pretty good code

# Making It All Work

#### Details

- LLIR is largely machine independent

- Target machine described as LLIR → ASM pattern

- Actual pattern matching

- → Use a hand-coded pattern matcher

(gcc)

- Several important compilers use this technology

- It seems to produce good portable instruction selectors

Key strength appears to be late low-level optimization

#### Instruction selection

- Mapping <u>IR</u> into assembly code

- Assumes a fixed storage mapping & code shape

- Combining operations, using address modes

#### Instruction scheduling

- Reordering operations to hide latencies

- Assumes a fixed program (set of operations)

- Changes demand for registers

#### Register allocation

- Deciding which values will reside in registers

- Changes the storage mapping, may add false sharing

- Concerns about placement of data & memory operations

# What Makes Code Run Fast?

- Operations have non-zero latencies

- Modern machines can issue several operations per cycle

- Execution time is order-dependent

#### What Makes Code Run Fast?

# Assumed latencies (conservative)

| <b>Operation</b> | Cycles |

|------------------|--------|

| load             | 3      |

| store            | 3      |

| loadl            | 1      |

| add              | 1      |

| mult             | 2      |

| fadd             | 1      |

| fmult            | 2      |

| shift            | 1      |

| branch           | 0 to 8 |

- Loads & stores may or may not block

- Non-blocking ⇒fill those issue slots

- Branch costs vary with path taken

- Scheduler should hide the latencies

|                          |    | Cycles     | Simple so | <u>chedule</u> |

|--------------------------|----|------------|-----------|----------------|

|                          | 1  | loadAl     | r0,@w     | ⇒ r1           |

|                          | 4  | add        | r1,r1     | ⇒ r1           |

| Load causes add to stall | 5  | loadAl     | r0,@x     | ⇒ r2           |

|                          | 8  | mult       | r1,r2     | ⇒ r1           |

|                          | 9  | loadAl     | r0,@y     | ⇒ r2           |

|                          | 12 | mult       | r1,r2     | ⇒ r1           |

|                          | 13 | loadAl     | r0,@z     | ⇒ r2           |

|                          | 16 | mult       | r1,r2     | ⇒ r1           |

|                          | 18 | storeAl    | r1        | ⇒ r0,@w        |

|                          | 21 | r1 is free |           |                |

2 registers, 20 cycles

|                           |    | Cycles     | Simple so | <u>:hedule</u> |

|---------------------------|----|------------|-----------|----------------|

|                           | 1  | loadAl     | r0,@w     | ⇒ r1           |

|                           | 4  | add        | r1,r1     | ⇒ r1           |

|                           | 5  | loadAl     | r0,@x     | ⇒ r2           |

|                           | 8  | mult       | r1,r2     | ⇒ r1           |

| Load causes mult to stall | 9  | loadAl     | r0,@y     | ⇒ r2           |

|                           | 12 | mult       | r1,r2     | ⇒ r1           |

|                           | 13 | loadAl     | r0,@z     | ⇒ r2           |

|                           | 16 | mult       | r1,r2     | ⇒ r1           |

|                           | 18 | storeAl    | r1        | ⇒ r0,@w        |

|                           | 21 | r1 is free |           |                |

2 registers, 20 cycles

|                           |    | Cycles     | Simple so | <u>chedule</u>     |            |

|---------------------------|----|------------|-----------|--------------------|------------|

|                           | 1  | loadAl     | r0,@w     | ⇒ r1               |            |

|                           | 4  | add        | r1,r1     | ⇒ r1               |            |

|                           | 5  | loadAl     | r0,@x     | ⇒ r2               |            |

|                           | 8  | mult       | r1,r2     | ⇒ r1               |            |

|                           | 9  | loadAl     | r0,@y     | ⇒ r2               |            |

|                           | 12 | mult       | r1,r2     | ⇒ r1               |            |

| Load causes mult to stall | 13 | loadAl     | r0,@z     | ⇒ r2               |            |

| bodd oddoos man io oran   | 16 | mult       | r1,r2     | <b>⇒</b> r1        |            |

|                           | 18 | storeAl    | r1        | $\Rightarrow$ r0,@ | <u>)</u> w |

|                           | 21 | r1 is free |           |                    |            |

2 registers, 20 cycles

|                           |    | Cycles     | Simple so | <u>chedule</u> |    |

|---------------------------|----|------------|-----------|----------------|----|

|                           | 1  | loadAl     | r0,@w     | ⇒ r1           |    |

|                           | 4  | add        | r1,r1     | ⇒ r1           |    |

|                           | 5  | loadAl     | r0,@x     | ⇒ r2           |    |

|                           | 8  | mult       | r1,r2     | ⇒ r1           |    |

|                           | 9  | loadAl     | r0,@y     | ⇒ r2           |    |

|                           | 12 | mult       | r1,r2     | <b>⇒</b> r1    |    |

|                           | 13 | loadAl     | r0,@z     | ⇒ r2           |    |

|                           | 16 | mult       | r1,r2     | ⇒ r1           |    |

| Load causes mult to stall | 18 | storeAl    | r1        | ⇒ r0,@         | )w |

|                           | 21 | r1 is free |           |                |    |

2 registers, 20 cycles

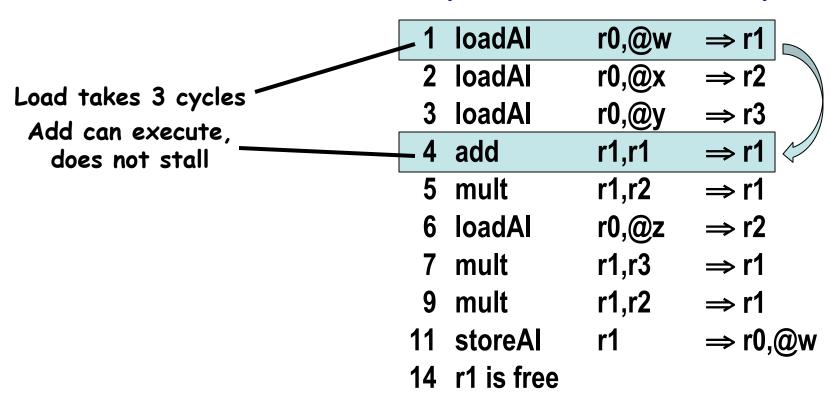

#### Cycles Schedule loads early

|                      | 1  | loadAl     | r0,@w | ⇒ r1    |

|----------------------|----|------------|-------|---------|

|                      | 2  | loadAl     | r0,@x | ⇒ r2    |

| Schedule loads early | 3  | loadAl     | r0,@y | ⇒ r3    |

|                      | 4  | add        | r1,r1 | ⇒ r1    |

|                      | 5  | mult       | r1,r2 | ⇒ r1    |

|                      | 6  | loadAl     | r0,@z | ⇒ r2    |

|                      | 7  | mult       | r1,r3 | ⇒ r1    |

|                      | 9  | mult       | r1,r2 | ⇒ r1    |

|                      | 11 | storeAl    | r1    | ⇒ r0,@w |

|                      | 14 | r1 is free |       |         |

|                      |    |            |       |         |

3 registers, 13 cycles

Reordering operations to improve some metric is called instruction scheduling

| Cycles   | Schedule   | loads                                   | early        |

|----------|------------|-----------------------------------------|--------------|

| <u> </u> | 2011011111 | *************************************** | <del> </del> |

3 registers, 13 cycles

Reordering operations to improve some metric is called instruction scheduling

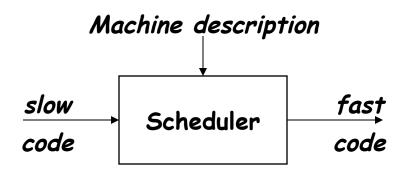

# Instruction Scheduling

(Engineer's View)

The Problem

Given a code fragment and the latencies for each operation, reorder the operations to minimize execution time

#### The Concept

#### The task

- Produce correct code

- Minimize wasted cycles

- Avoid spilling registers

- Operate efficiently

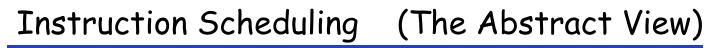

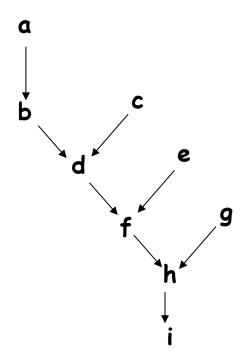

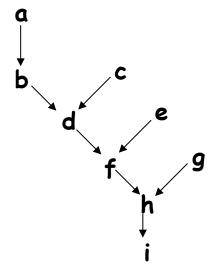

To capture properties of the code, build a dependence graph G

- Nodes  $n \in G$  are operations

- An edge  $e = (n_1, n_2) \in G$  if  $n_2$  uses the result of  $n_1$

| a: | loadAl  | r0,@w | ⇒ r1                |

|----|---------|-------|---------------------|

| b: | add     | r1,r1 | ⇒ r1                |

| C: | loadAl  | r0,@x | ⇒ r2                |

| d: | mult    | r1,r2 | ⇒ r1                |

| e: | loadAl  | r0,@y | ⇒ r2                |

| f: | mult    | r1,r2 | ⇒r1                 |

| g: | IoadAl  | r0,@z | ⇒ r2                |

| h: | mult    | r1,r2 | ⇒ r1                |

| i: | storeAl | r1    | $\Rightarrow$ r0,@w |

The Code

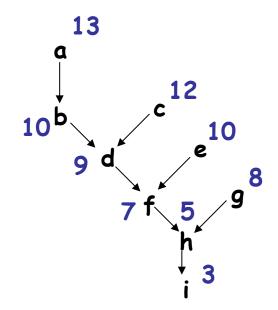

The Dependence Graph

- All operands must be available

- Multiple operations can be <u>ready</u>

- Moving operations can lengthen register lifetimes

- → Increases register pressure

- Operands can have multiple predecessors

Together, these issues make scheduling <u>hard</u>

(NP-complete)

# Instruction Scheduling (Local list scheduling)

- 1. Build a dependence graph, P

- 2. Compute a <u>priority function</u> over the nodes in P

- 3. Use list scheduling to construct a schedule, one cycle at a time

- a. Use a queue of operations that are ready

- b. At each cycle

- I. Choose a ready operation and schedule it

- II. Update the ready queue

```

DIVERSITYON ELAWARE

```

```

Cycle ← 1

Active ← Ø

Ready ← roots of P

```

Initialize and set roots as ready to schedule.

```

while (Ready \cup Active \neq \emptyset)

if (Ready \neq \emptyset) then

remove an op from Ready

S(op) \leftarrow Cycle

Active \leftarrow Active \cup op

Cycle ← Cycle + 1

for each op \in Active

if (S(op) + delay(op) \le Cycle) then

remove op from Active

for each successor s of op in P

if (s is ready) then

Ready \leftarrow Ready \cup s

```

Cycle  $\leftarrow$  1

Active  $\leftarrow$  Ø

Ready  $\leftarrow$  roots of P

while (Ready ∪ Active ≠ Ø)

if (Ready ≠ Ø) then

remove an op from Ready

S(op) ← Cycle

Active ← Active ∪ op

Cycle ← Cycle + 1

for each op ∈ Active

if (S(op) + delay(op) ≤ Cycle) then

remove op from Active

for each successor s of op in P

if (s is ready) then

Ready ← Ready ∪ s

Loop while ready queue is not empty. Remove an op from ready queue to schedule (move to active)

```

Cycle ← 1

Active ← Ø

Ready ← roots of P

while (Ready ∪ Active ≠ Ø)

if (Ready ≠ Ø) then

remove an op from Ready

S(op) ← Cycle

Active ← Active ∪ op

```

Cycle ← Cycle + 1

for each op ∈ Active

if (S(op) + delay(op) ≤ Cycle) then

remove op from Active

for each successor s of op in P

if (s is ready) then

Ready ← Ready ∪ s

Simulating architecture; increment cycle count

```

Cycle ← 1

Active ← Ø

Ready ← roots of P

while (Ready ∪ Active ≠ Ø)

if (Ready ≠ Ø) then

remove an op from Ready

S(op) ← Cycle

Active ← Active ∪ op

Cycle ← Cycle + 1

```

for each op ∈ Active if (S(op) + delay(op) ≤ Cycle) then remove op from Active

for each successor s of *op* in P if (s is ready) then Ready ← Ready ∪ s

Check if operations in Active queue should be removed based on cycle count.

```

Cycle ← 1

Active \leftarrow \emptyset

Ready \leftarrow roots of P

while (Ready \cup Active \neq \emptyset)

if (Ready \neq \emptyset) then

remove an op from Ready

S(op) \leftarrow Cycle

Active \leftarrow Active \cup op

Cycle ← Cycle + 1

for each op \in Active

if (S(op) + delay(op) \le Cycle) then

remove op from Active

```

for each successor s of *op* in P ,

if (s is ready) then

Ready ← Ready ∪ s

If successor's operands are ready, put it on Ready queue

# DIVERSITY OF ELAWARE

# 1. Build the dependence graph

| a: | loadAl  | r0,@w | ⇒ r1    |

|----|---------|-------|---------|

| b: | add     | r1,r1 | ⇒ r1    |

| c: | loadAl  | r0,@x | ⇒ r2    |

| d: | mult    | r1,r2 | ⇒ r1    |

| e: | loadAl  | r0,@y | ⇒ r2    |

| f: | mult    | r1,r2 | ⇒ r1    |

| g: | loadAl  | r0,@z | ⇒ r2    |

| h: | mult    | r1,r2 | ⇒ r1    |

| i: | storeAl | r1    | ⇒ r0,@w |

The Code

The Dependence Graph

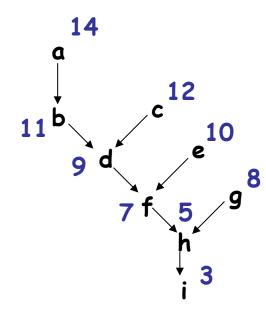

# Scheduling Example

- 1. Build the dependence graph

- 2. Determine priorities: longest latency-weighted path

| a: | loadAl  | r0,@w | ⇒ r1    |

|----|---------|-------|---------|

| b: | add     | r1,r1 | ⇒ r1    |

| c: | loadAl  | r0,@x | ⇒ r2    |

| d: | mult    | r1,r2 | ⇒ r1    |

| e: | loadAl  | r0,@y | ⇒ r2    |

| f: | mult    | r1,r2 | ⇒ r1    |

| g: | loadAl  | r0,@z | ⇒ r2    |

| h: | mult    | r1,r2 | ⇒ r1    |

| i: | storeAl | r1    | ⇒ r0,@w |

The Code

The Dependence Graph

# Scheduling Example

- 1. Build the dependence graph

- 2. Determine priorities: longest latency-weighted path

- 3. Perform list scheduling

- 1) a: loadAl r0,@w ⇒ r1 r0,@x **⇒** r2 2) c: loadAl r0,@y ⇒ r3 3) e: loadAl  $r1,r1 \Rightarrow r1$ 4) b: add r1,r2 ⇒ r1 5) d: mult  $r0,@z \Rightarrow r2$ 6) g: loadAl 7) f: mult  $r1,r3 \Rightarrow r1$ 9) h: mult r1,r2 ⇒ r1

The Code

r1

⇒ r0,@w

11) i: storeAl

#### New register name used

The Dependence Graph

#### List scheduling breaks down into two distinct classes

#### Forward list scheduling

- Start with available operations

- · Work forward in time

- Ready ⇒ all operands available

#### Backward list scheduling

- Start with no successors

- Work backward in time

- Ready ⇒ result >= all uses